CXL, RiscV, IB, DPA

Interconnect buzzword bingo, ACES workshop 2024

Troy Benjegerdes <network@7el.us>

Agtech: What's old is new again

- 150 acres in Iowa

- generational repair & maintenance requirements

- sustainable biomass for HPC

Title Text

- Bullet One

- Bullet Two

- Bullet Three

Future farm robots

In-field repair is a first-class design requirement

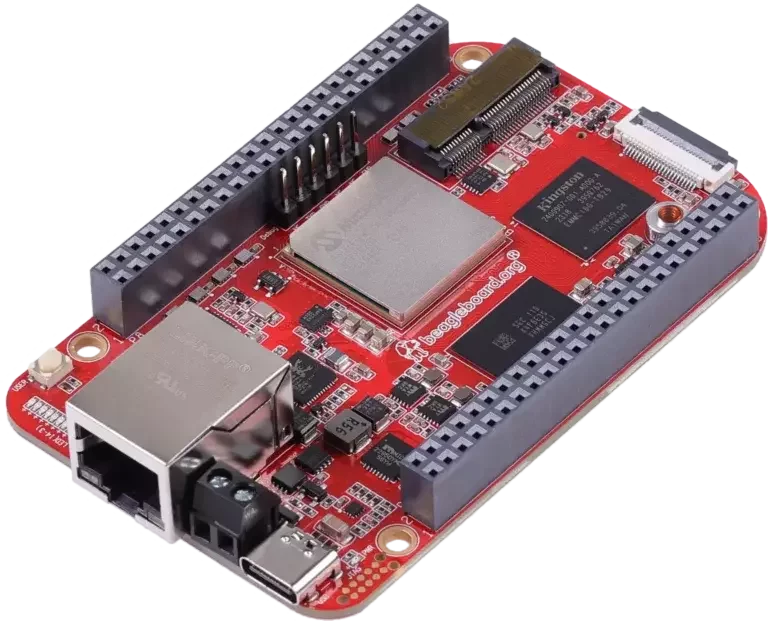

- RiscV inside (done)

- Industrial InfiniBand (in-progress)

- HPC backend for AI model training (future work)

- Education and rural economic development

RiscV inside

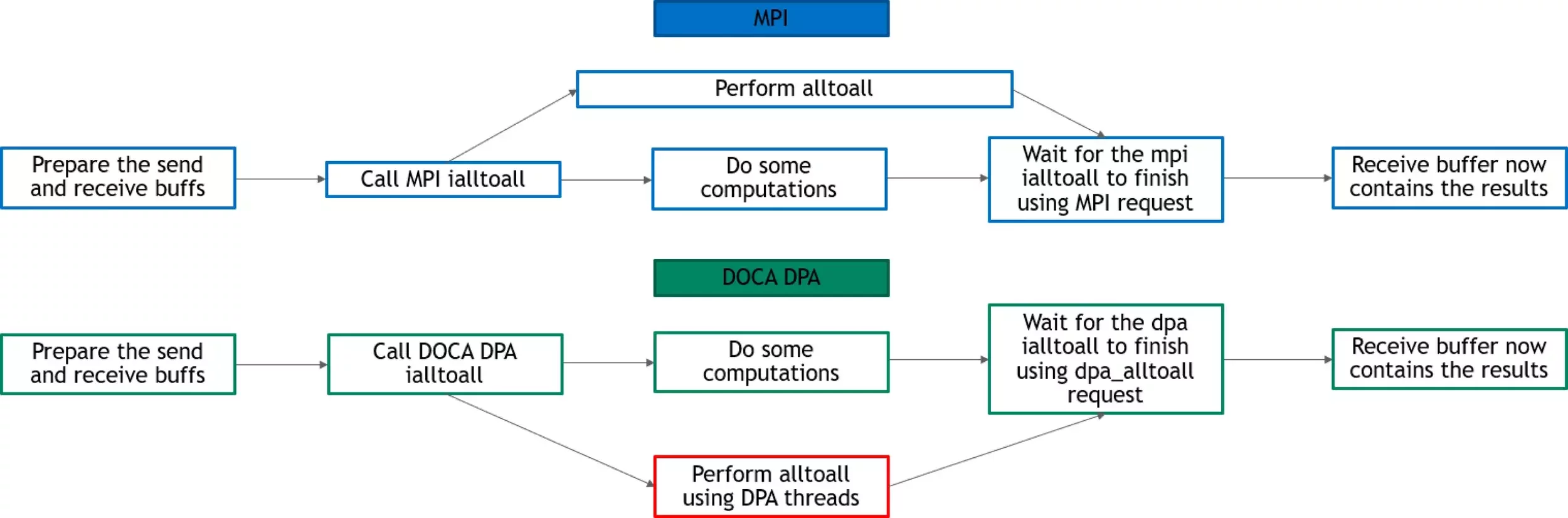

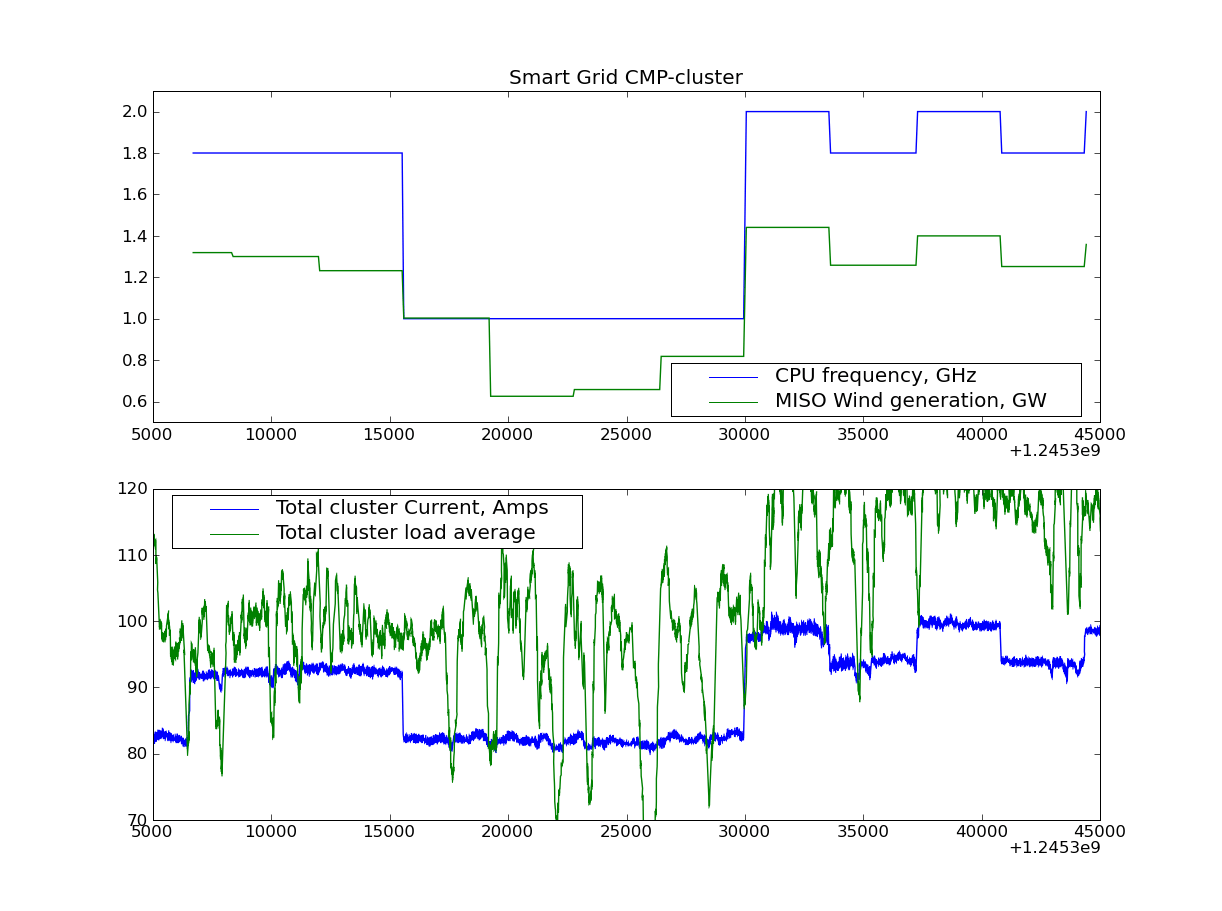

Make addition associative again!

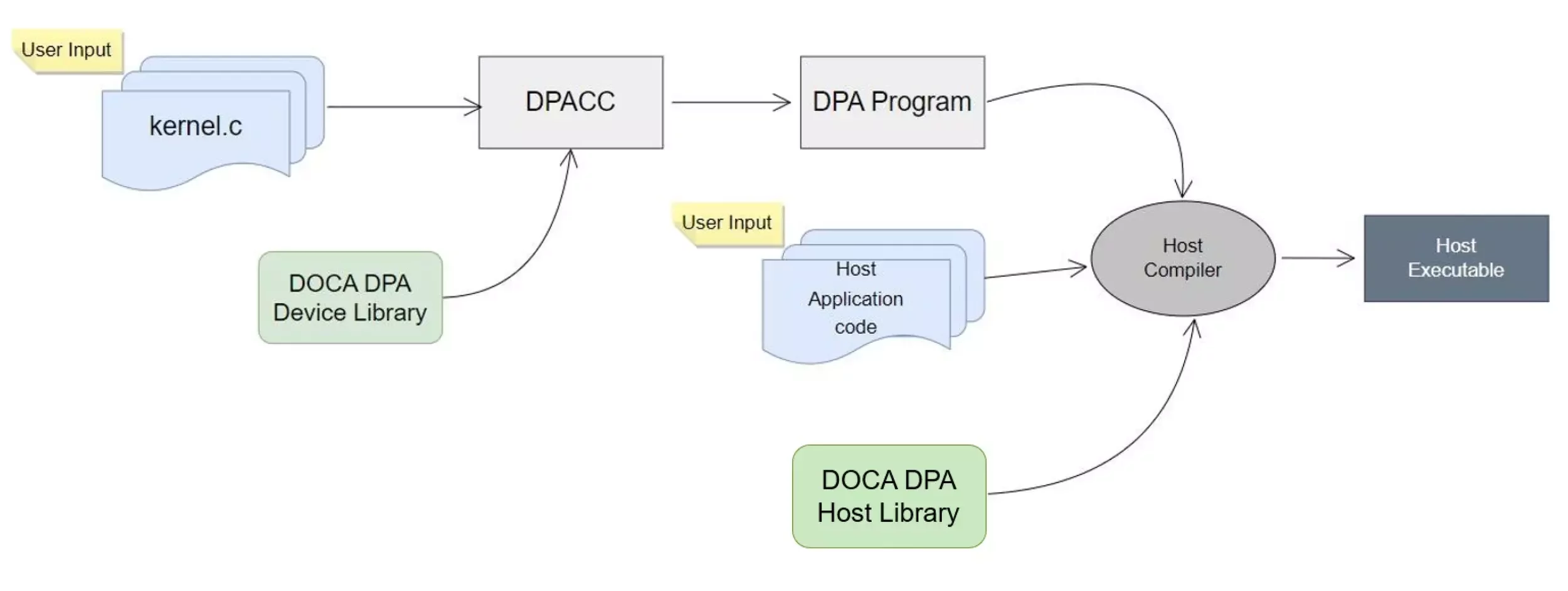

- Use the DPA to read float/double

- software conversion to FP16/BF16/posit

- Make parallel addition associative again

- posit + quire (32 bits + 512 bit 'quire' accumulator)

- deterministic round-off [1]

- Kulisch accumulators [2]

- DPA writes back collective result as IEEE float/double

Current work:

Tunga posit hardware

- https://calligotech.com/tunga/

- 28nm 8-core Rocket-chip, Berkley hardfloat replaced with Calligo Tech posit implementation

- software and application support still very early stage

What would Patterson do?

Can we do architecture research on:

- Intel x86 - NO

- Arm - sure, with an NDA and an architecture license

- RiscV - YES, if you build a whole new instruction set

Can we do network interconnect research on:

- Cray/HPE Slingshot --- NO

- Broadcom PEX89000 --- ???

- Nvidia QM9790 -- ???

- Microchip PolarFire SOC -- yes, but only to 12Gbps