Components of a Computer and their Uses

Recap

1.Give a definition for the Fetch-Decode-Execute cycle?

2.Name the 6 components of a processor. (full names not the abbreviations)

3.What happens to the PC after every cycle?

4.Where is the contents of the MDR copied to in the cycle?

Learning Objectives

•Describe the factors affecting the performance of the CPU: clock speed, number of cores, cache

•Understand the use of pipelining in a processor to improve efficiency

Buses

Address bus:

The address bus is uni-directional.

It is only concerned with passing an address one way, from the CPU to the RAM.

The only thing it needs to do is to identify the address of the location in the cache or main memory that is to be read from or written to.

The address bus is measured by the number of bits it can hold, 8, 16, 32, 64.

The wider the address bus is, the more memory spaces there are available. Therefore, increasing the maximum amount of primary storage.

Buses

Data bus:

The data bus is bi-directional.

It can carry data to the main memory from the processor and vice versa.

The data bus will transfer data to and from the address that is held on the address bus.

The amount of data that can be carried by the data bus depends on the word size. Word size describes the width of the data bus. Typically 8, 16, 32 or 64 bits wide.

The wider the bus is, the faster data can be transferred.

Buses

Data bus:

The data bus is bi-directional.

It can carry data to the main memory from the processor and vice versa.

The data bus will transfer data to and from the address that is held on the address bus.

The amount of data that can be carried by the data bus depends on the word size. Word size describes the width of the data bus. Typically 8, 16, 32 or 64 bits wide.

Factors affecting performance

The main factors affecting the processor performance are:

- The clock speed of the processor

- The number of cores in the processor

- The amount and type of cache memory

Factors affecting performance

The Fetch-Decode-Execute cycle is triggered by the clock pulses of the system clock

The faster the clock speed, the faster a computer can fetch, decode and execute instructions

- This clock can change state many billions of times per second

- A 4GHz processor would tick 4 billion times per second!

Complete the worksheet in your notebooks, titled "Buses and Improving the performance of a processor"

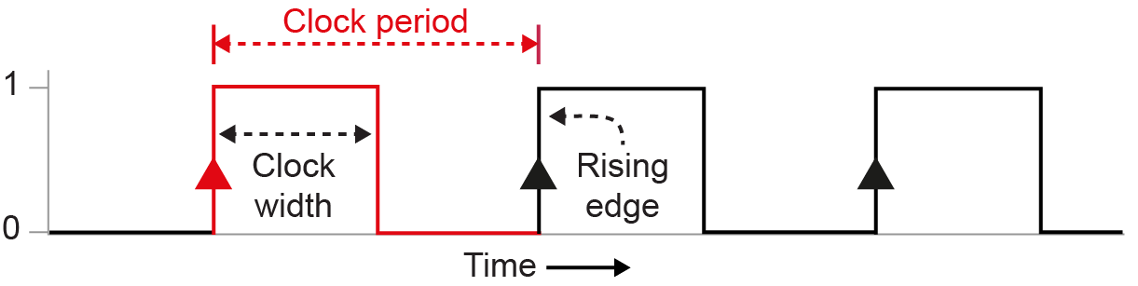

The System Clock

- A series of regular ON/OFF signals are used to synchronise the operations of the processor components.

- Actions are usually carried out on the rising edge of the clock

- actions each take a fixed number of cycles to complete

The Number of Cores

- Many computers today, including personal computers, have multiple cores

- A dual-core computer has two processors linked together in the same integrated circuit

- A quad-core computer has four linked processors

- Each core is theoretically able to process a different instruction at the same time with its own fetch-decode-execute cycle, making a quad core computer four times faster than a single-core computer

- However, the software may not always be able to take full advantage of all four processors

Parallel processing

- Using several processor cores working at the same time is known as parallel or concurrent processing

- In systems designed for parallel processing, each core can work concurrently on different parts on the same task

- BUT, because instructions are processed sequentially, this is not always possible

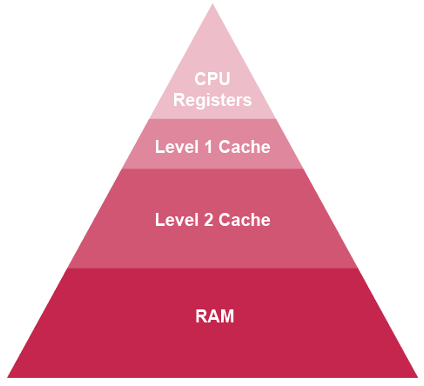

Cache memory

- The cache is a small amount of super fast memory that stores data and instructions that have been recently used by the processor

- However, it is rather expensive because of how it improves the performance of the processor

Cache memory

- Level 1 cache memory is split into instruction cache and data cache, so that data and instructions can be fetched simultaneously

- The more cache memory a computer has, the more likely it is that it will not have to fetch the next instruction or data from the RAM

Pipelining

- This is a technique used to improve the performance of the processor by, for example, overlapping stages in the fetch-decode-execute cycle, or by breaking down the stages in an arithmetic instruction

- An instruction enters the pipeline, and as soon as one stage has been completed, another instruction enters the pipeline

- A third instruction can then enter before either one of the others is completed

- There may be 10 or 12 stages in the pipeline, stored in a buffer close to the processor, waiting to move onto the next step