數位電路&CPU

計算機概論[1]

講師:溫室蔡、乘一

電腦簡史

「computer」

原指「從事計算的人」

電腦被發明的目的

就是為了用來處理大量的計算

電腦簡史

19 世紀初:巴貝奇的差分機

19 世紀末:何樂禮的打孔製表機

二戰:破解德軍密碼的巨像電腦

戰後:計算火炮彈道的 ENIAC

關鍵元件

要控制電子電路只能靠「開關」

要自動化得靠「能被其他電路控制的開關」

於是就發展出了:

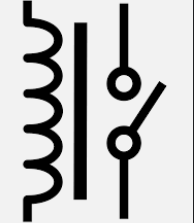

繼電器

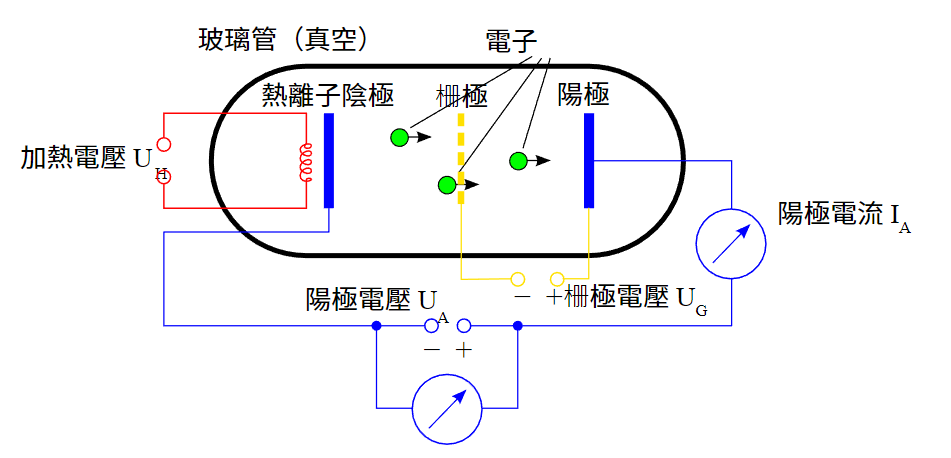

真空管

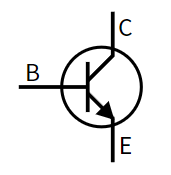

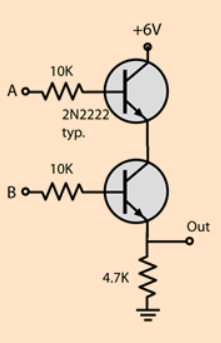

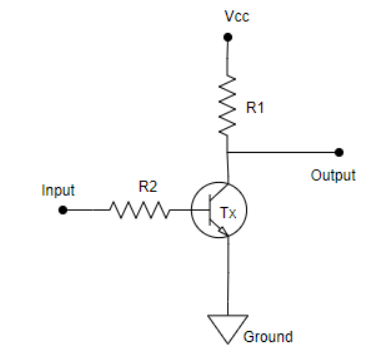

電晶體

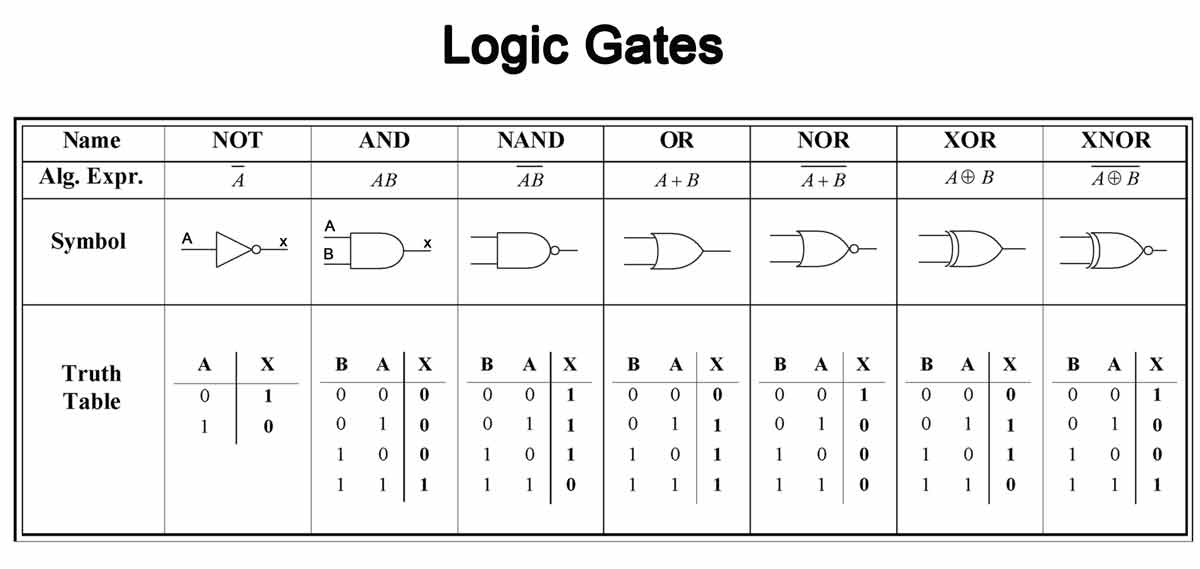

邏輯閘

現代電腦以電晶體為基礎

進一步構成了可處理二元輸入/輸出的邏輯閘

邏輯閘

數學上而言,只用 NOT 跟 AND

就能做出剩下的所有邏輯閘

NOT 閘

AND 閘

邏輯閘

就可以開始設計用來進行數學運算的電路了

有了這些邏輯閘之後

但在那之前…

如何表示數字

我們則將其定義為 1 跟 0

並以「二進制」來表示數字

數位電路中只存在「開」跟「關」

8 4 2 1

1 1 0 1

如何表示數字

8 4 2 1

1 1 0 1

8×1 + 4×1 + 2×0 + 1×1 = 13

8 4 2 1

1 1 0 1

那負數呢?

如果我們要表示負數

我們會把最高位的值改成負的

-8 4 2 1

1 1 0 1

那負數呢?

如果我們要表示負數

我們會把最高位的值改成負的

-8×1 + 4×1 + 2×0 + 1×1 = -3

這樣的好處是負數可以直接數到正數

加法器

二進制的加法有如下的真值表:

| 輸入 A | 輸入 B | 總和 | 進位 |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

如何用邏輯閘做出來?

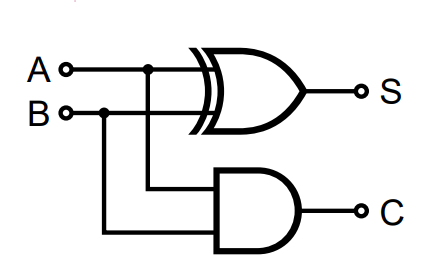

加法器

二進制的加法有如下的真值表:

| 輸入 A | 輸入 B | 總和 | 進位 |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

如何用邏輯閘做出來?

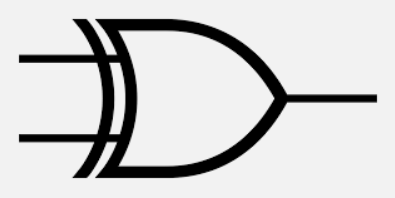

XOR

加法器

二進制的加法有如下的真值表:

| 輸入 A | 輸入 B | 總和 | 進位 |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

如何用邏輯閘做出來?

AND

加法器

於是可以像這樣做出一個「半加器」:

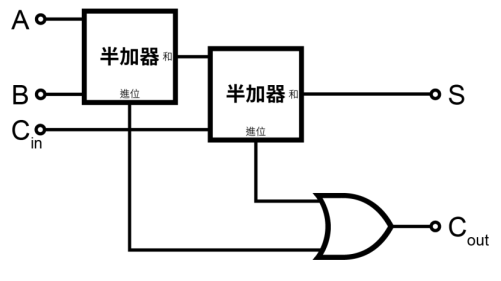

加法器

但實際在運算的時候,因為有進位

會需要一次把三個數字加在一起

這時可以將兩個半加器組合在一起

做出「全加器」

加法器

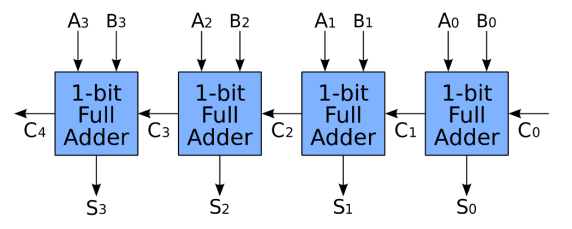

加法器

把 n 個全加器串連起來

就可以做出 n 位元加法器

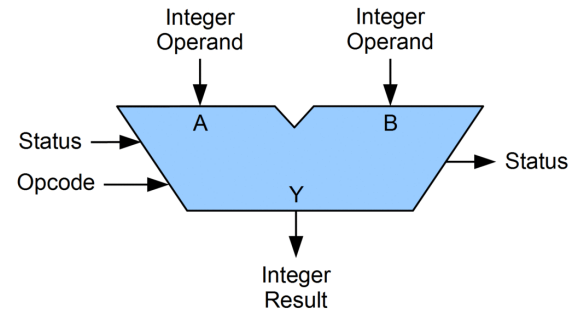

算術邏輯單元

在 CPU 中,算術邏輯單元(ALU)

用來對兩個數字進行算術或邏輯運算

算術邏輯單元

ALU 可以用「操作碼」(opcode)

從多種運算中選擇一種執行,如:

-

加法

-

減法

-

帶進位加法

-

帶進位減法

-

AND

-

OR

-

XOR

-

變號

-

加 1

-

減 1

-

左移

-

右移

算術邏輯單元

除了輸出計算結果外

ALU 還會輸出一些「狀態」,如:

-

結果是不是零?

-

結果是不是負數?

-

結果有沒有進位?

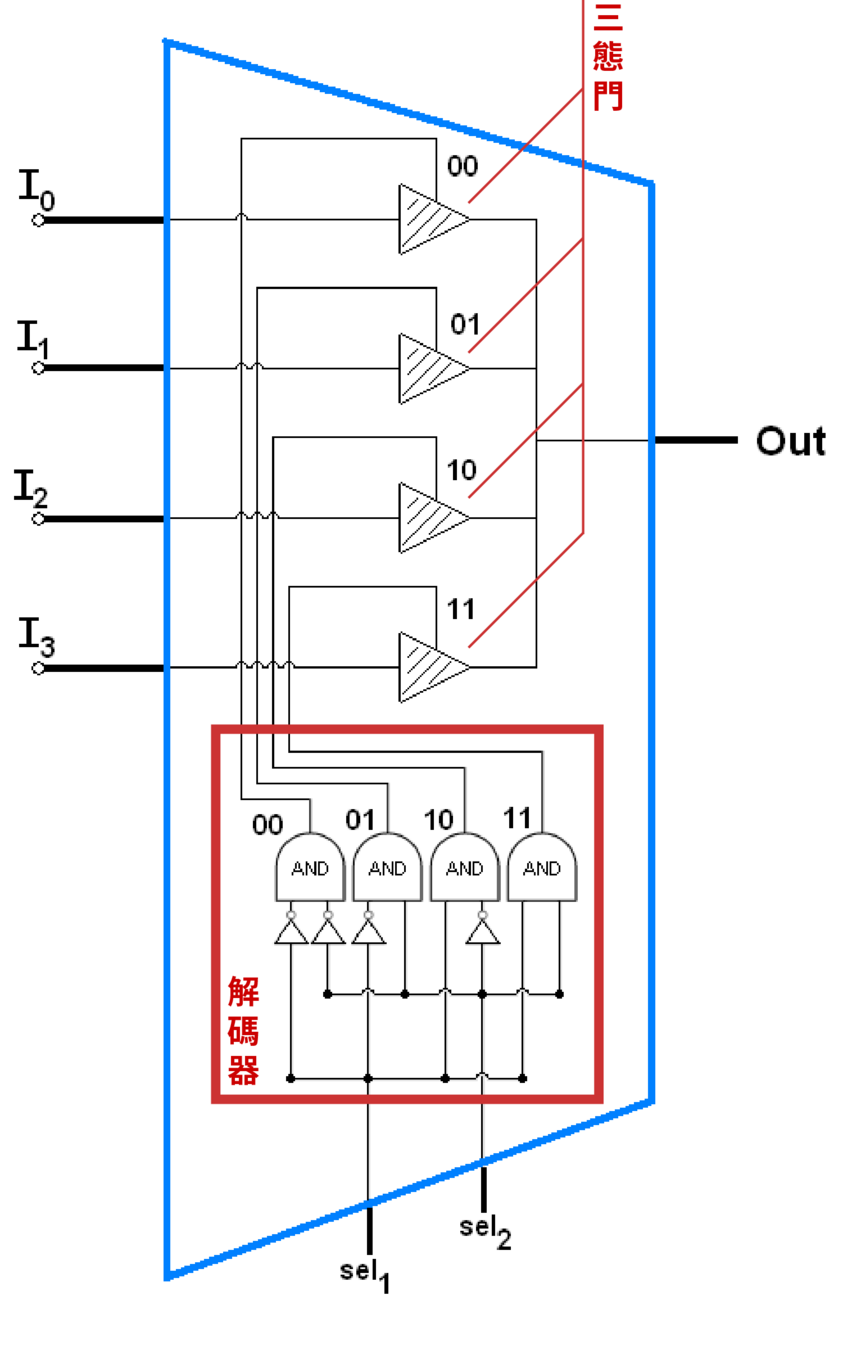

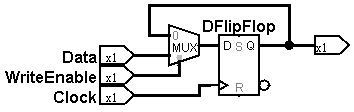

多工器

多工器(Multiplexer)

經常縮寫為 MUX

可以從多個輸入中

選擇其中一個做為輸出

可用來選擇 ALU 的操作

儲存元件

計算結果如果不能儲存就沒有意義了

因此需要建立一種在特定條件下

即使輸入改變

也不會影響輸出狀態的電路

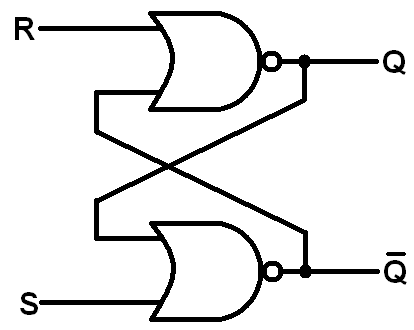

SR 閂鎖

SR 指的是 Set 跟 Reset

它可以選擇儲存一個 1(Set)

或儲存一個 0(Reset)

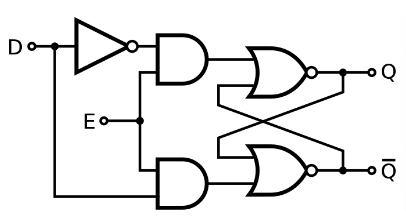

門控 D 閂鎖

在 SR 閂鎖外再加入一層

控制存 1 或存 0 的「Data」(D)

以及控制是否儲存的「門控」(E)

| D | E | SR 輸入 |

|---|---|---|

| X | 0 | 無 |

| 0 | 1 | Reset |

| 1 | 1 | Set |

無窮迴圈

如果把 D 閂鎖儲存的值拿去做運算

再試圖將結果存回 D 閂鎖

會導致無窮迴圈

這時就需要引入「時脈」與「正反器」

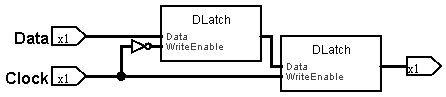

D 正反器

可以將兩個 D 閂鎖如下結合

神奇地,現在只有在時脈輸入由 0 轉 1 時

資料才會更新

暫存器

為 D 正反器加上門控後

就得到了 CPU 中最重要的暫存器

隨機存取記憶體

就像加法器一樣

暫存器也可以串聯來儲存 n 位元的數字

但更重要的是

如果將大量的 n 位元暫存器排成矩陣

再用另一條輸入決定要存取的暫存器

就做出了隨機存取記憶體(RAM)

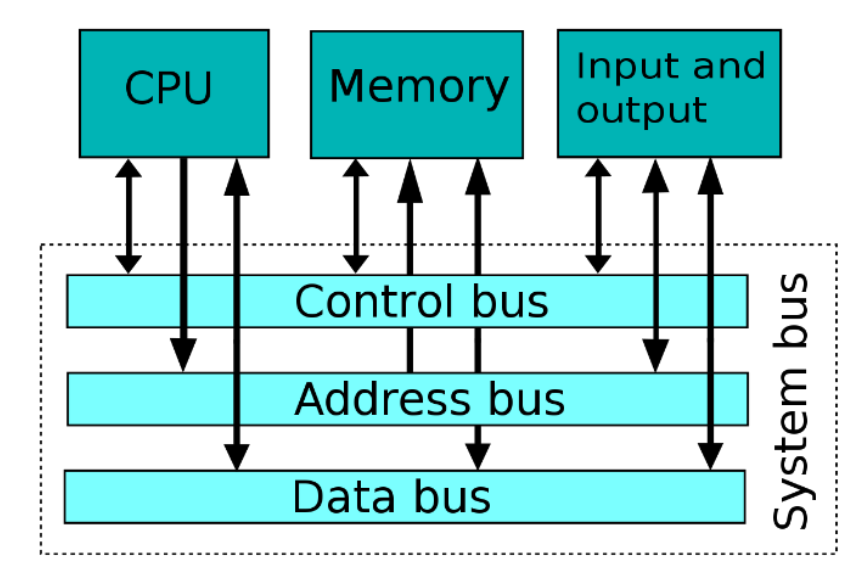

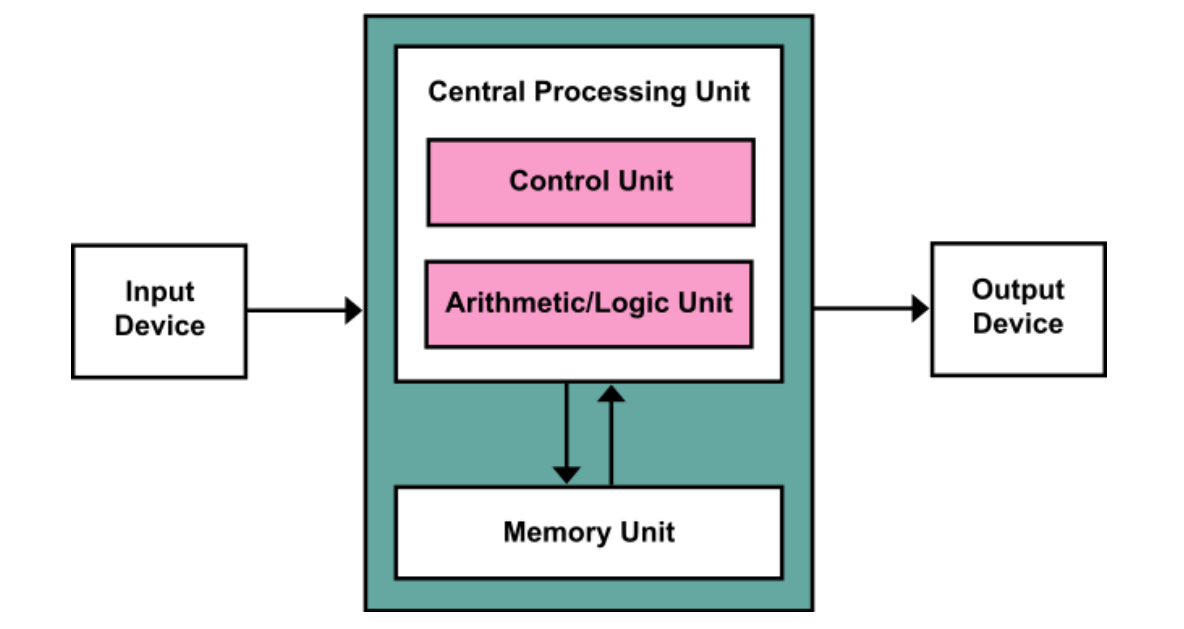

馮紐曼架構

CPU 負責控制其他元件進行運算

記憶體則負責儲存程式與其資料

兩者之間透過匯流排(Bus)溝通

這是現今多數電腦的架構

稱為「馮紐曼架構」

(Von Neumann architecture)

馮紐曼架構

匯流排

CPU 中的多個元件要相互溝通

讀取或寫入彼此的資料

為避免線路複雜

所有的元件共用同一條線路

稱為匯流排(Bus)

匯流排