Timeloop

Overview

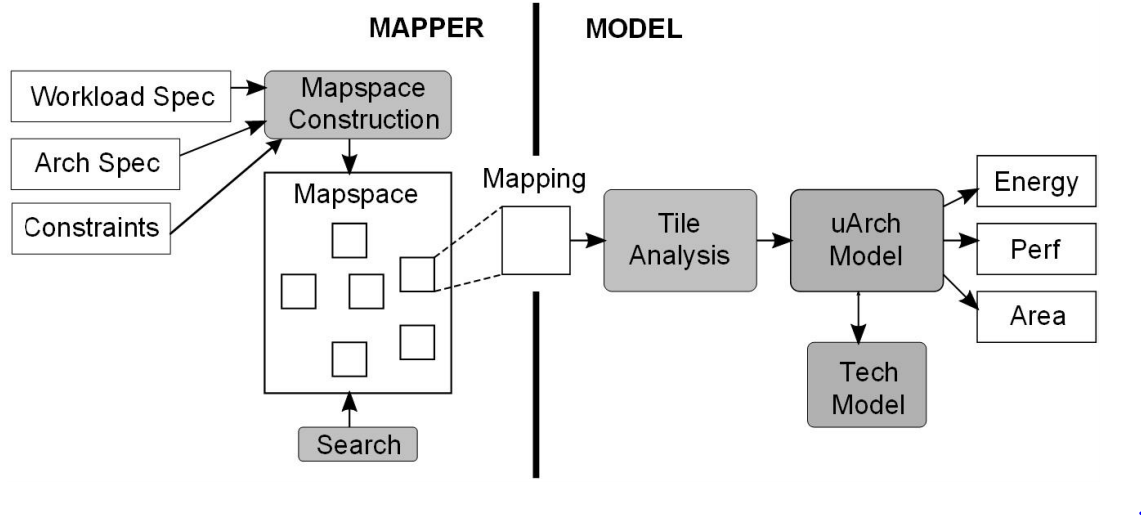

- Infrastructure to evaluate the arch. design space of DNN accelerators

- Emulation to estimate performance and energy

- Mapper to generate schedule and stage data

Key Takeaway: co-design of dataflow and memory hierarchy is crucial for energy efficiency.

Model

- Specify the architecture in a abstract way

- Model estimates perf & energy numbers

- Abstraction supports specifying compute, memory and connections in a hierarchical way

Mapper

- constructs mapspace for a given hw config

- evaluates the quality of each mapping using a cost-model

- Searches the mapspace iteratively for optimal mapping

Motivation

-

Model needs a mapper

- Unlike a general purpose ISA, a single output can be computed in multiple ways in DNN accelerators

- Finding optimal mapping among many possibilities is crucial

- Optimal mapping can be computed for a (workload, architecture) pair

-

Mapper needs a model

- Searching through the mapspace requires a cost-model to compare different mappings

Overall Flow

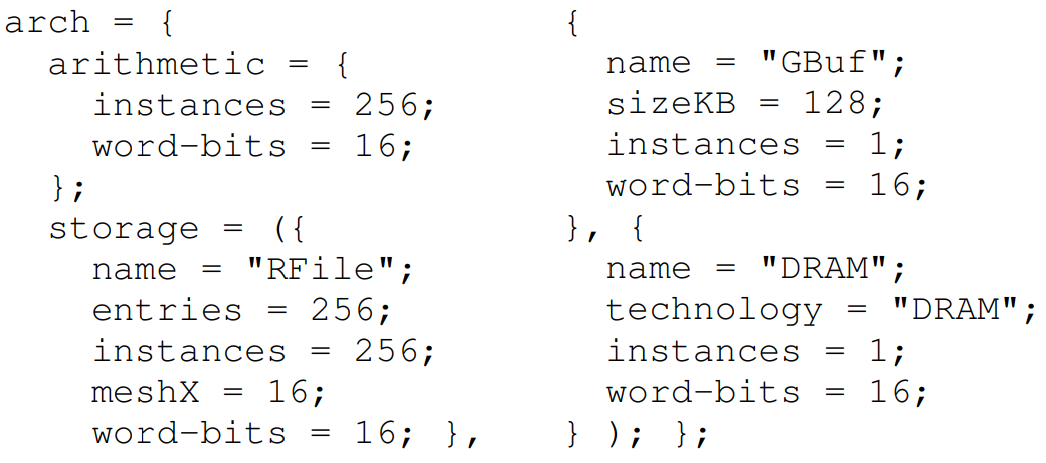

Arch Representation