ORGANIZACIÓN AVANZADA DE MEMORIAS RAM

Arquitectura de Computadores

Sol Hernandez Conde

Andres Banda Vega

Leidys Cordero Espitia

Sebastian Arteaga Lopez

MEMORIA PRINCIPAL SEMICONDUCTORA

1. Dos estados estables: para representar al uno (1) y al cero (0).

2. Se puede escribir en ellas, al menos una vez

3. Se pueden leer para conocer el estado.

La celda de memoria.

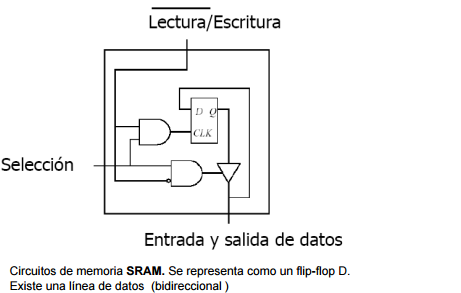

– (SRAM) Basada en flip flops: memoria estática

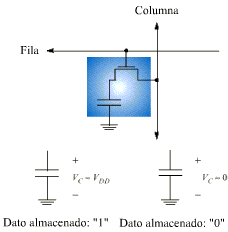

– (DRAM) Basada en transistores: memoria dinámica

Acceso aleatorio

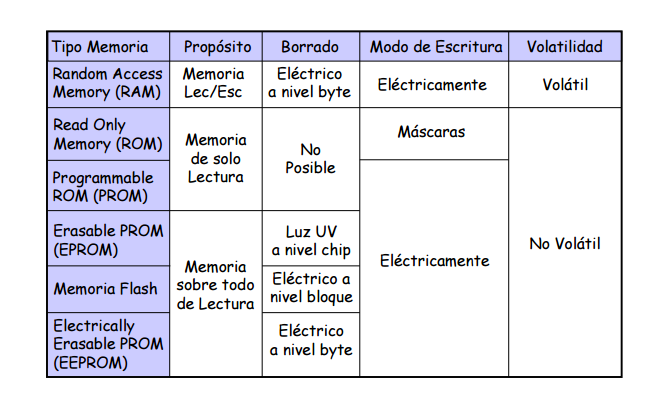

TIPOS DE MEMORIA

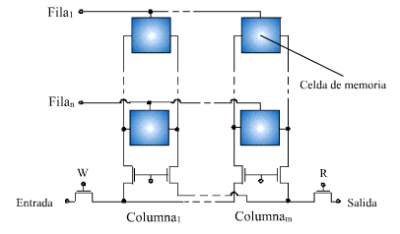

ORGANIZACIÓN

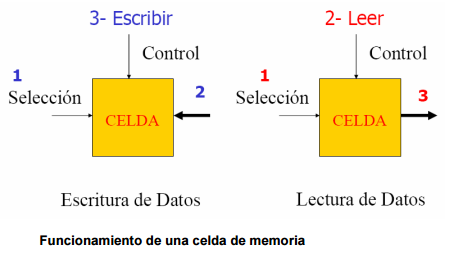

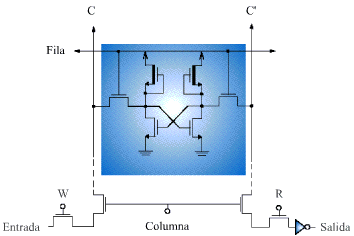

En general la celda tiene 4 terminales funcionales capaces de llevar una señal eléctrica:

1. Selección: selecciona una celda de memoria.

2. Control: especifica lectura ó escritura.

3. Escritura: Proporciona la señal que fija el estado de la celda a 0 o 1.

4. Lectura de datos: El tercer terminal se utiliza como salida del estado de la celda.

Funcionamiento

CELDA DE MEMORIA

Celda de RAM Dinámica

Microprocesadores Memoria RAM dinámica La operación de la celda es similar a la de un interruptor, cuando el estado en la fila se encuentra en alto, el transistor entra en aturación y el dato presente en el bus interno de la memoria (columna) se almacena en el condensador, durante una operación de escritura y se extrae en una operación de lectura.

Celda de RAM Estatica

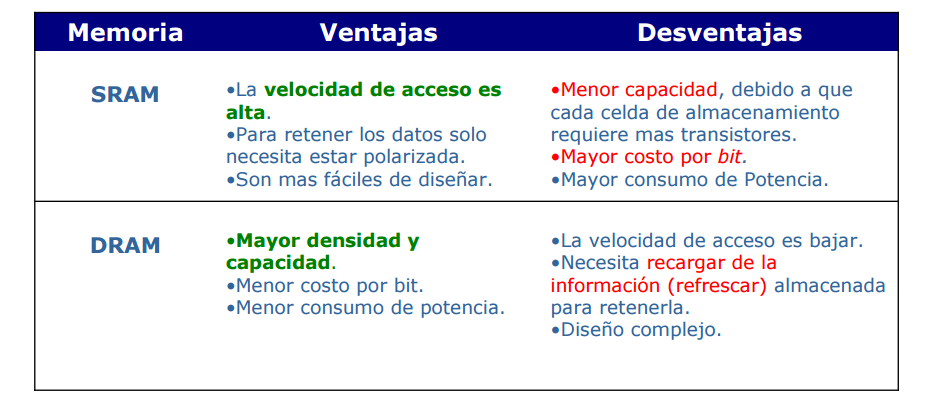

SRAM vs DRAM

• Ambas son volatiles.

– Debe aplicarse continuamente tensión de alimentaciòn para mantener los valores de los bits

• DRAM: Dynamic cell

– Mas simple de construir, mas pequeña

– Mas densas (celdas mas pequeñas = mas celdas por unidad de superficie).

– Menos caras

– Necesita circuiteria para realizar el refresco. – Son las preferidas para memorias grandes.

• Static ( SRAM)

– Un poco mas rapidas.

– Se utilizan como memorias Cache

SRAM vs DRAM

ROM

• Contiene un patrón permanente de datos que no puede alterarse.

• No requiere fuente de alimentacion para mantener memorizados los valores de los bits.

• Es posible leer de una ROM pero no escribir datos en ella.

• Se utiliza en microprogramación.

• Subrutinas de biblioteca para funciones de uso frecuente

• Programas del sistema

• Tablas de funciones

TIPOS DE ROM

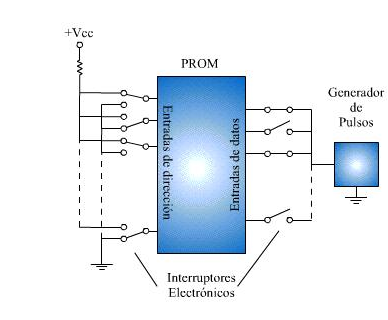

PROM

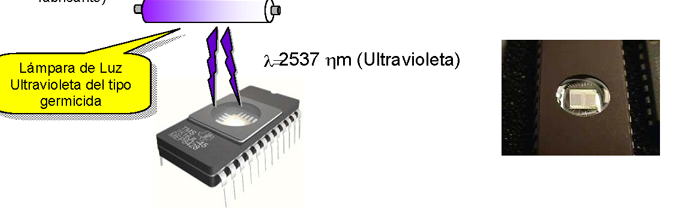

EPROM

Las EPROM se programan insertando el chip en un programador de EPROM. aplicando en un pin especial de la memoria una tensión entre 10 y 25 Voltios durante aproximadamente 50 ms, según el dispositivo, al mismo tiempo se direcciona la posición de memoria y se pone la información a las entradas de datos.

EEPROM

Las memorias EEPROM (Electrically Erasable Programmable Read-onlyMemory) son memorias no volátiles y eléctricamente borrables a nivel de bytes. La posibilidad de programar y borrar las memorias a nivel de bytes supone una gran flexibilidad, pero también una celda de memoria más compleja. Además del transistor de puerta flotante anterior, es preciso un segundo transistor de selección.

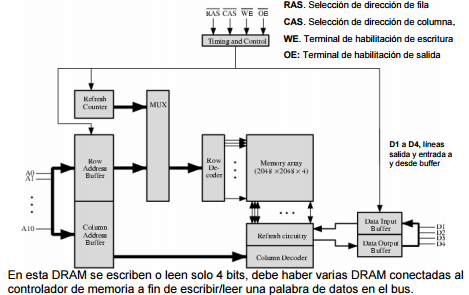

ORGANIZACION TIPICA DE DRAM 16MB

TIPOS DE DRAM

•SDRAM: DRAM síncrona

•DDR_RAM: SDRAM de doble velocidad.

•RDRAM Rambus: Adoptada por Intel para sus procesadores Pentium e Itanium.

•Ambas implican el uso del reloj del sistema para facilitar la transferencia de bloques de datoss.

DRAM sincrona

La SDRAM se sincroniza con el reloj de la computadora para permitirle enviar instrucciones más eficientemente al unirse con otras instrucciones que la computadora esté procesando. El acopio de información en una computadora permite que reciba otro comando antes de haber terminado de procesar el anterior. Esto permite que la SDRAM opera a velocidades más alta, haciéndola la forma más popular de RAM ofrecida en las computadoras.

DDR SDRAM

DDR son las siglas para Doble Tasa de Transferencia de Datos, y es la memoria que evoluciona de la SDRAM. De manera análoga a la SDRAM, DDR es síncrona con el reloj del sistema teniendo como principal diferencia que la DDR RAM puede leer datos en los ejes de subida y bajada de la señal de reloj, mientras que la SDRAM únicamente lo hace en el eje de subida de una señal. Básicamente esto permite que un módulo de DDR RAM pueda transferir datos al doble de velocidad que la SDRAM.

RDRAM Rambus

La RAMBus o RDRAM es un paso revolucionario de la SDRAM. Es un diseño de memoria con cambios en la estructura del transporte de datos. La RAMBus envía menos información en el transporte de datos, que es de 16 o 18 bits contra el estándar de 64 o 72, pero envía datos con mayor frecuencia. También lee datos en los ejes de subida y bajada de la señal de reloj como la DDR RAM.

REFERENCIAS BIBLIOGRAFICAS

•http://www.fdi.ucm.es/profesor/mendias/512/docs/tema12.pdf

•http://exa.unne.edu.ar/informatica/arquitectura/archivos/Unidad_6.pdf