The Life of a Bit

for (int i = 0; i <= 3; i += 2)

{

--i;

}C for Loop

for (int i = 0; i <= 3; i += 2)

--i;Assembly for Loop

asm

{

mov REX,0;

jmp END;

START: sub REX, 1;

add REX, 2;

END: cmp REX, 3;

jle START; --Jump if <=

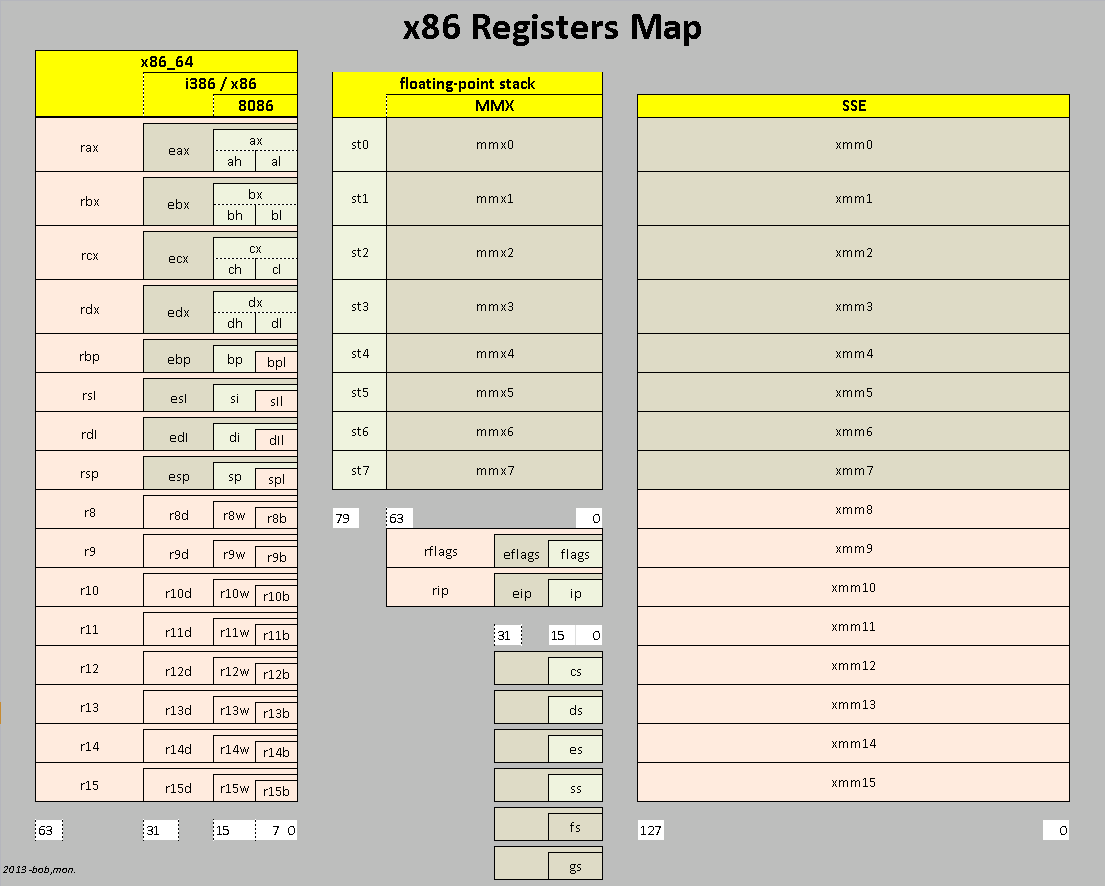

}Registers

Assembly to Opcodes

5: 48 BB 00 00 00 00 00 00 00 00 mov rbx,0x0

f: EB 08 jmp 19 <END>

11: 48 83 EB 01 sub rbx,0x1

15: 48 83 C3 02 add rbx,0x2

19: 48 83 FB 03 cmp rbx,0x3

1d: 7E F2 jle 11 <START>Deconstruction of Sub Instruction

48 83 EB 01 sub rbx,0x101001000 10000011 11101011 00000001Using 64-bit registers & Using extended registers

Group Code

Immediate Value

11 101 011Subtract

RBX

Going Deeper!

Arithmetic Logic Unit (ALU)

ALU in VHDL

entity Alu is

port ( aValue : in std_logic_vector(31 downto 0);

bValue : in std_logic_vector(31 downto 0);

operator : in std_logic_vector(2 downto 0);

resultValue : out std_logic_vector(31 downto 0);

zeroValue : out std_logic;

set : out std_logic;

overflow : out std_logic

);

end Alu;ALU in VHDL

architecture rtl of Alu is

begin

Alu_p: process(aValue,bValue,operator)

variable a,b,result : std_logic_vector(31 downto 0);

variable signOfA, signOfB : std_logic;

begin

a := aValue;

b := bValue;

signOfA := aValue(31);

signOfB := bValue(31);

if operator(2) = '1' then

b := NOT bValue;

end if;

--0000 and; 0001 or; 0010 add; 0110 subtract; 0111 set lt; 1100 nor

case operator(1) is

when '0' =>

case operator(0)is

when '0' => --000 AND Operation

if operator(2) = '1' then --100 NOR Operation. If we inverted B then invert A

a := NOT aValue;

end if;

result := a and b;

overflow <= '0';

when others =>

result := a or b; --X01 OR Operation

overflow <= '0';

end case;

when others =>

case operator(0)is

when '0' =>

if operator(2) = '1' then

b := b + 1; --110 SUB

end if;

result := a + b; --010 ADD

if operator(2) = '1' then -- Subtraction check for overflow

if (signOfA = '0' and signOfB = '1' and result(31) = '1') or

(signOfA = '1' and signOfB = '0' and result(31) = '0')

then -- Overflow has occurred

overflow <= '1';

else

overflow <= '0';

end if;

else --Addition Occurred. Check for overflow

if (signOfA = '0' and signOfB = '0' and result(31) = '1') or

(signOfA = '1' and signOfB = '1' and result(31) = '0')

then -- Overflow has occurred

overflow <= '1';

else

overflow <= '0';

end if;

end if;

when others =>

if aValue < bValue then --X11 SLT Funct

result := "00000000000000000000000000000001";

else

result := "00000000000000000000000000000000";

end if;

overflow <= '0';

end case;

end case;

resultValue <= result;

if (result = 0) then

zeroValue <= '1';

else

zeroValue <= '0';

end if;

set <= result(31);

end process Alu_p;

end rtl;Entering the Gates!

Let's Talk Gates

NOT

AND

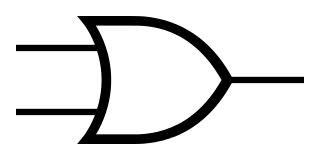

OR

XOR

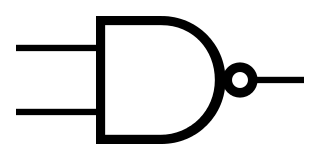

NAND

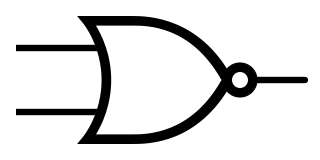

NOR

SR Latch

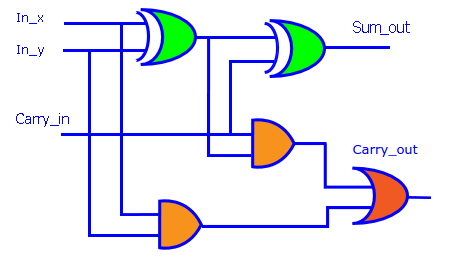

Full-Adder

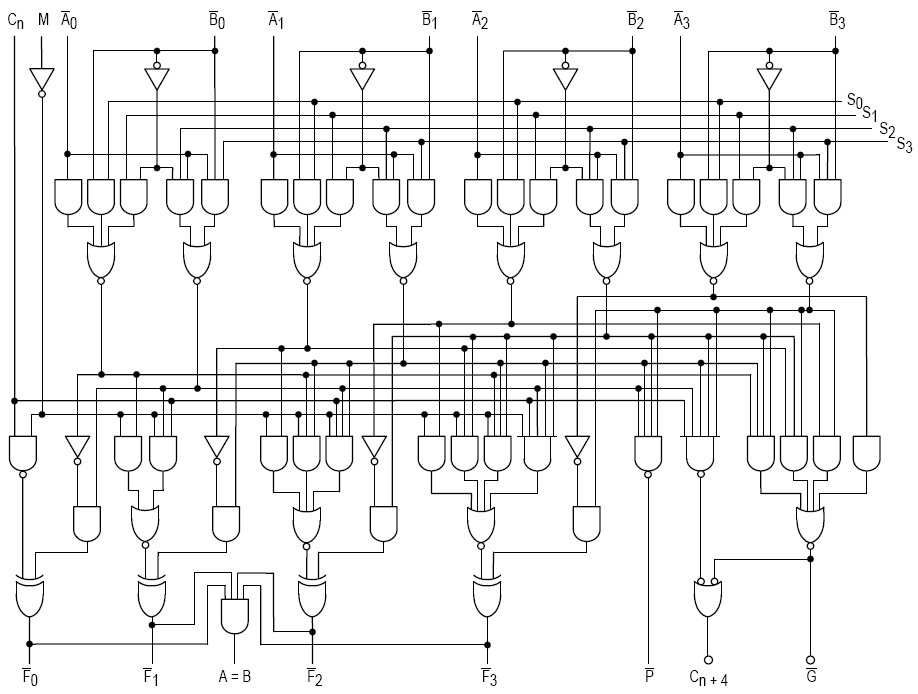

4-Bit ALU

Questions?