Project

Design a Folded-cascode OpAmp

The Schematic

Get id from gain, bandwidth, and slew rate

- Bandwidth & Gain

For target bandwidth,

- Slew Rate

- Let I1 - Iss <= 0, so I2 can be minimize.

- Also SR- = I2 / Cout

- Slew Rate (Continue)

Let's recall previous result,

Then, the minimal requirement will be,

More about gain

Now, gm1 is known, gain is given, Rout can be calculated.

Let

More about gain (Continue)

More about gain (Continue)

Let

More about gain (Continue)

Skip the calculation...

Text

More about gain (Continue)

All ro can be modeled as functions of Rout

when k, m, n are set

In my case, k = 6, m = 1.9, n = 4.

From ro to gate length

Vds can be set and Id is known, we can calculate lambda.

From gate length to width

From model parameters,

The Initial Design

I write an auto-generation tool, so complicated hand calculation can be avoided.

The tool is open-source:

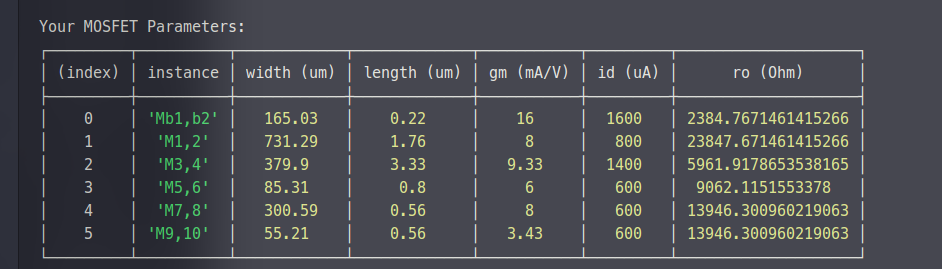

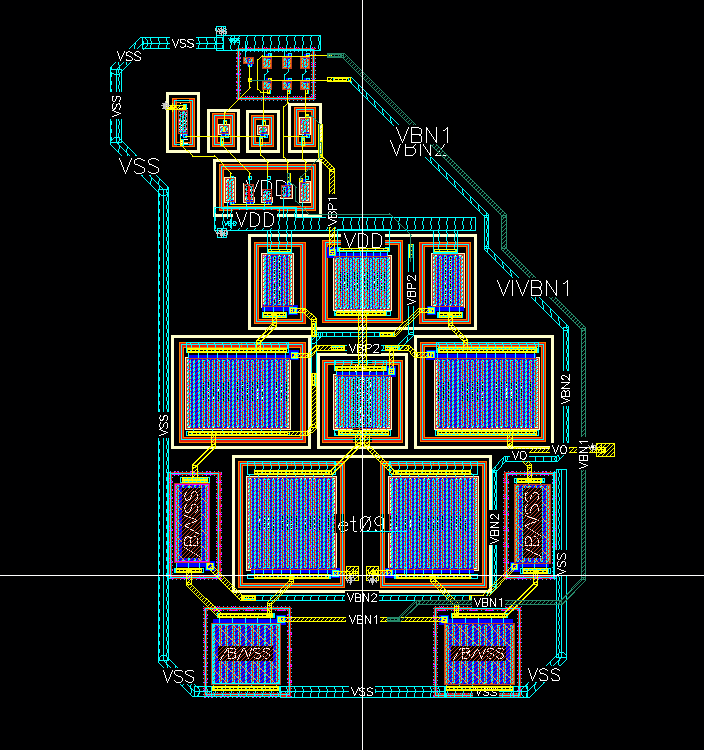

The Final Design after fine-tuning

Mb1,b2: w=165u, l=0.22u

M1,2: w=360u, l=0.5u

M3,4: w=130u, l=0.9u

M5,6: w=85u, l=0.8u

M7,8: w=300u, l=0.56u

M9,10: w=55u, l=0.56u

Id1,2 = 700uA

Id5-10 = 515uA

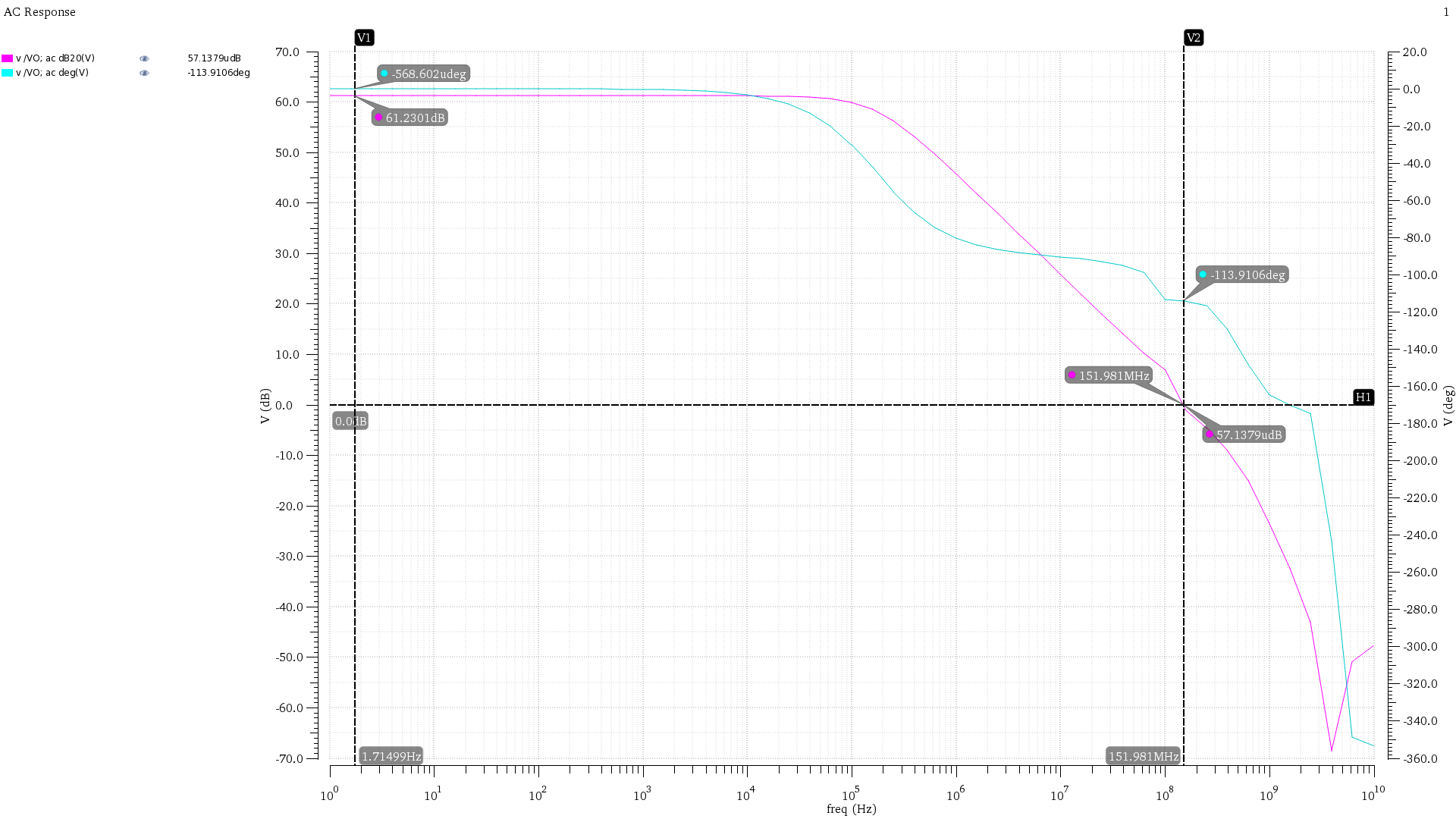

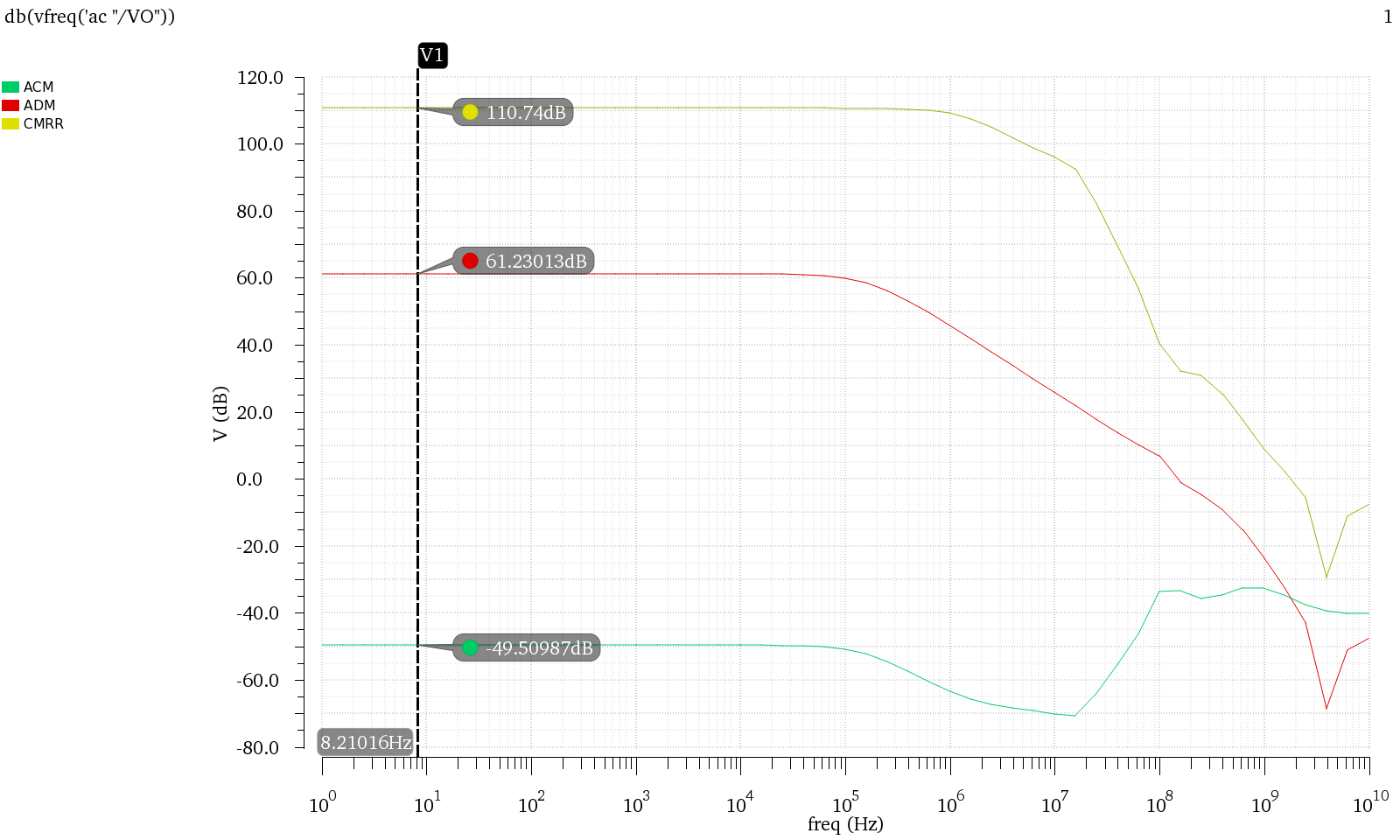

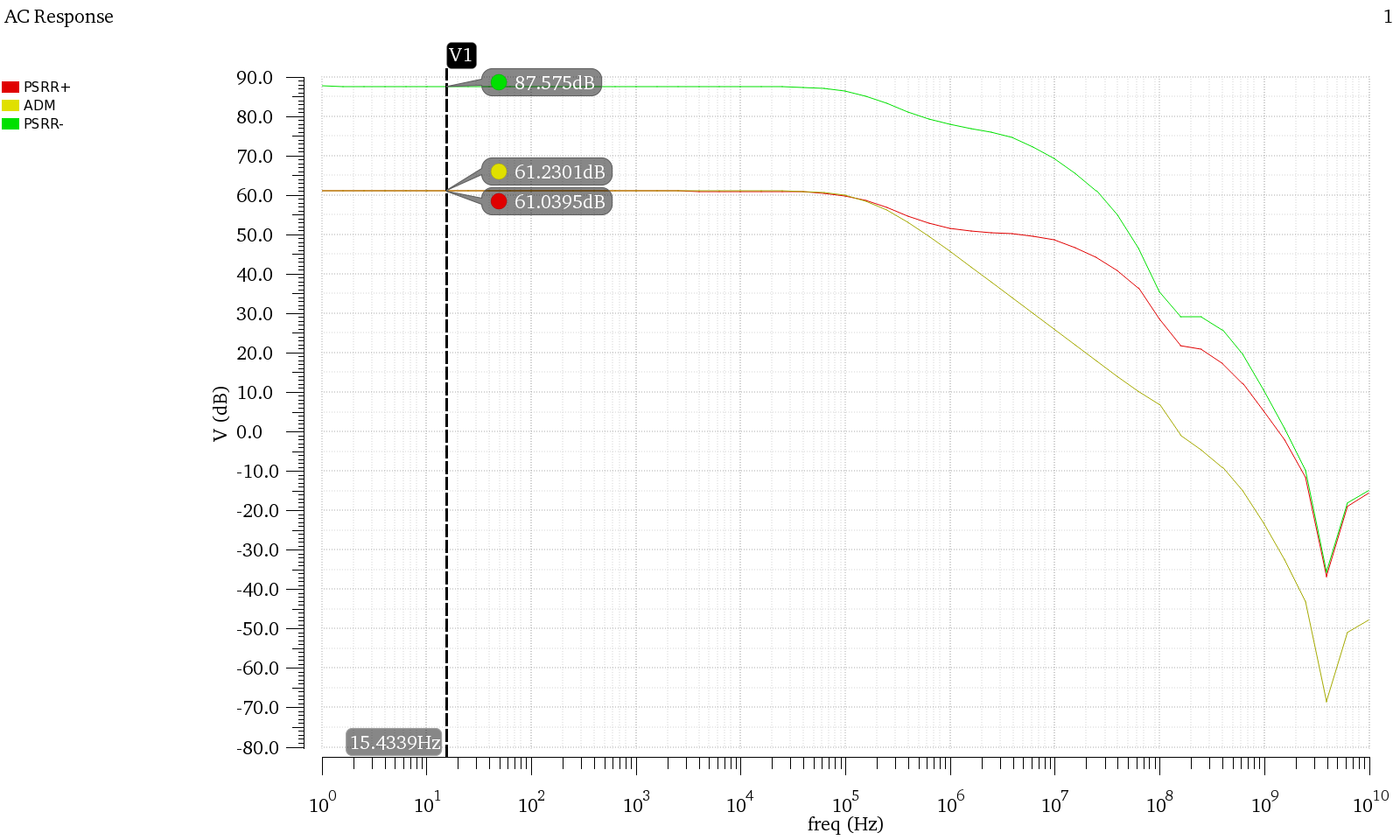

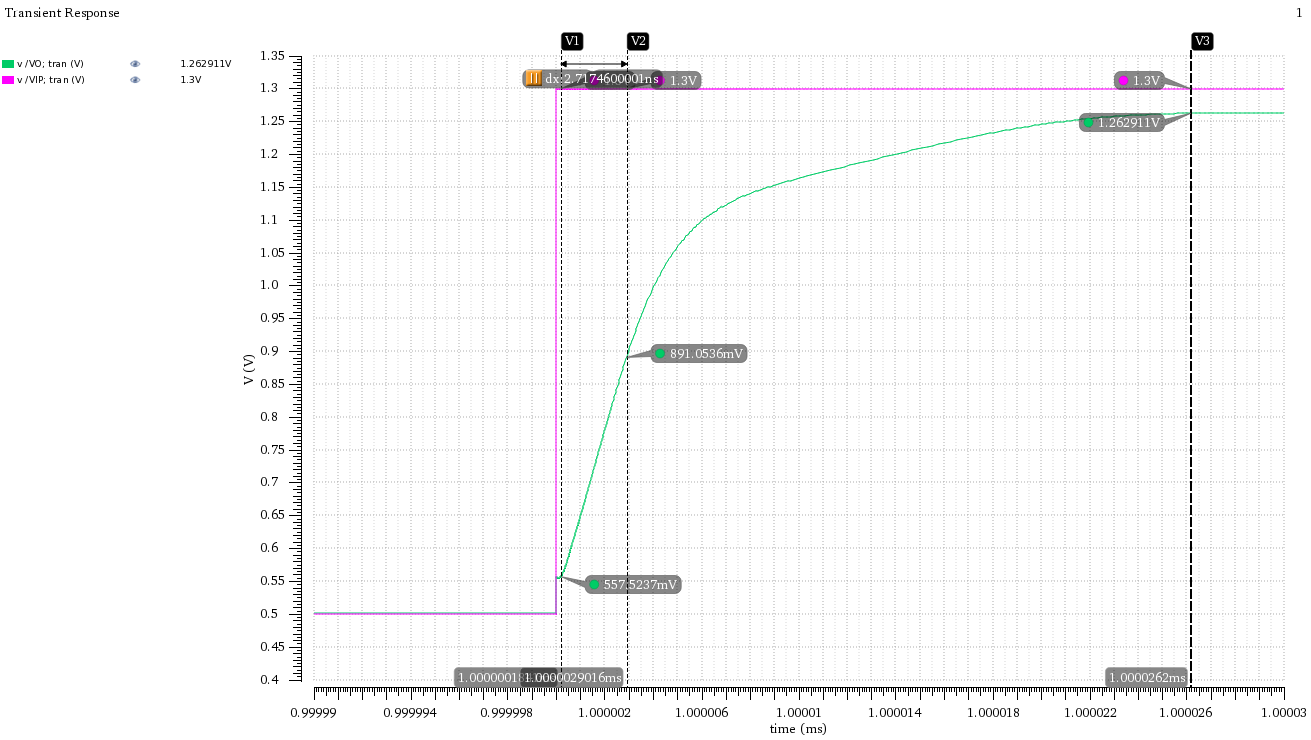

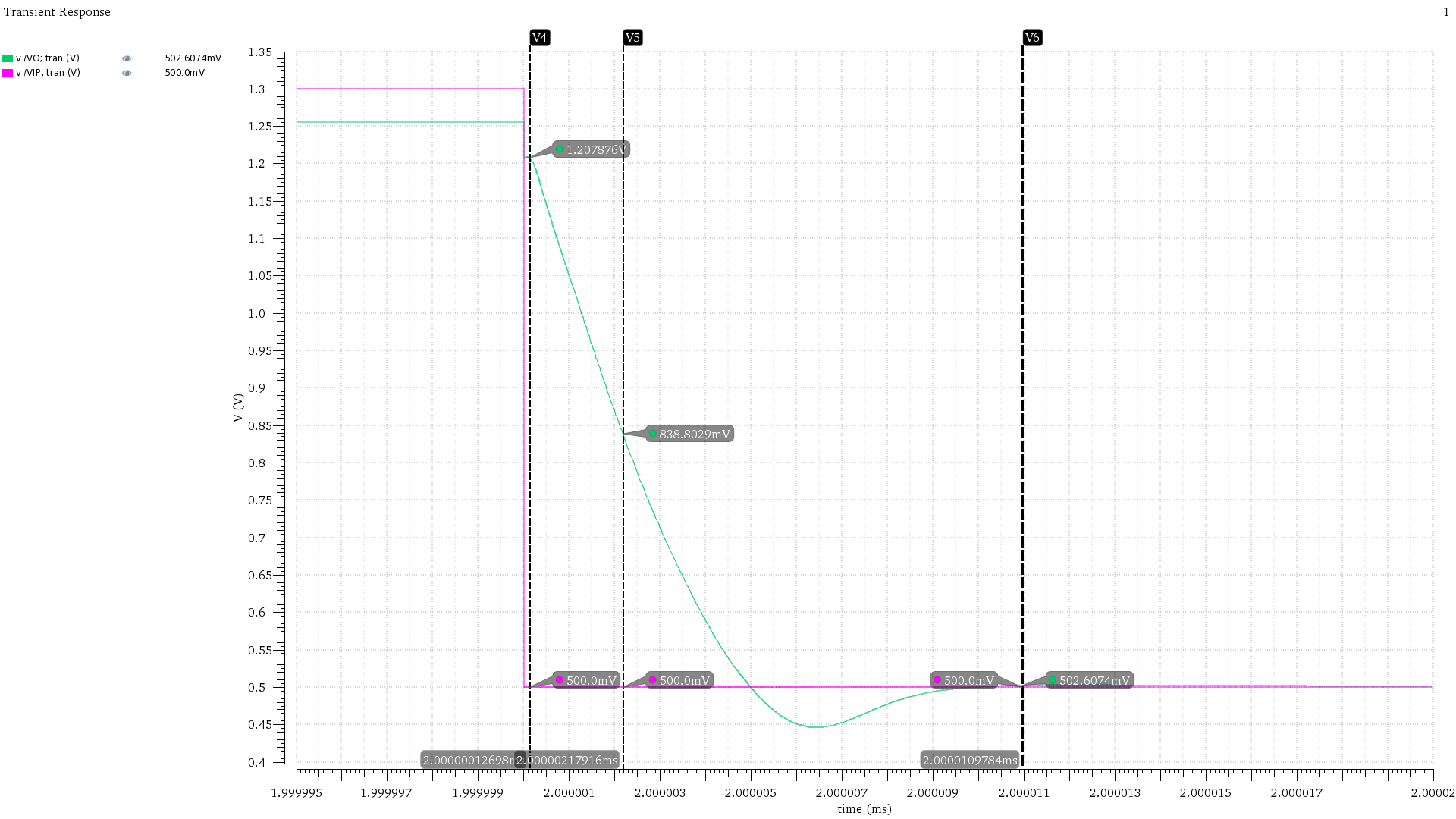

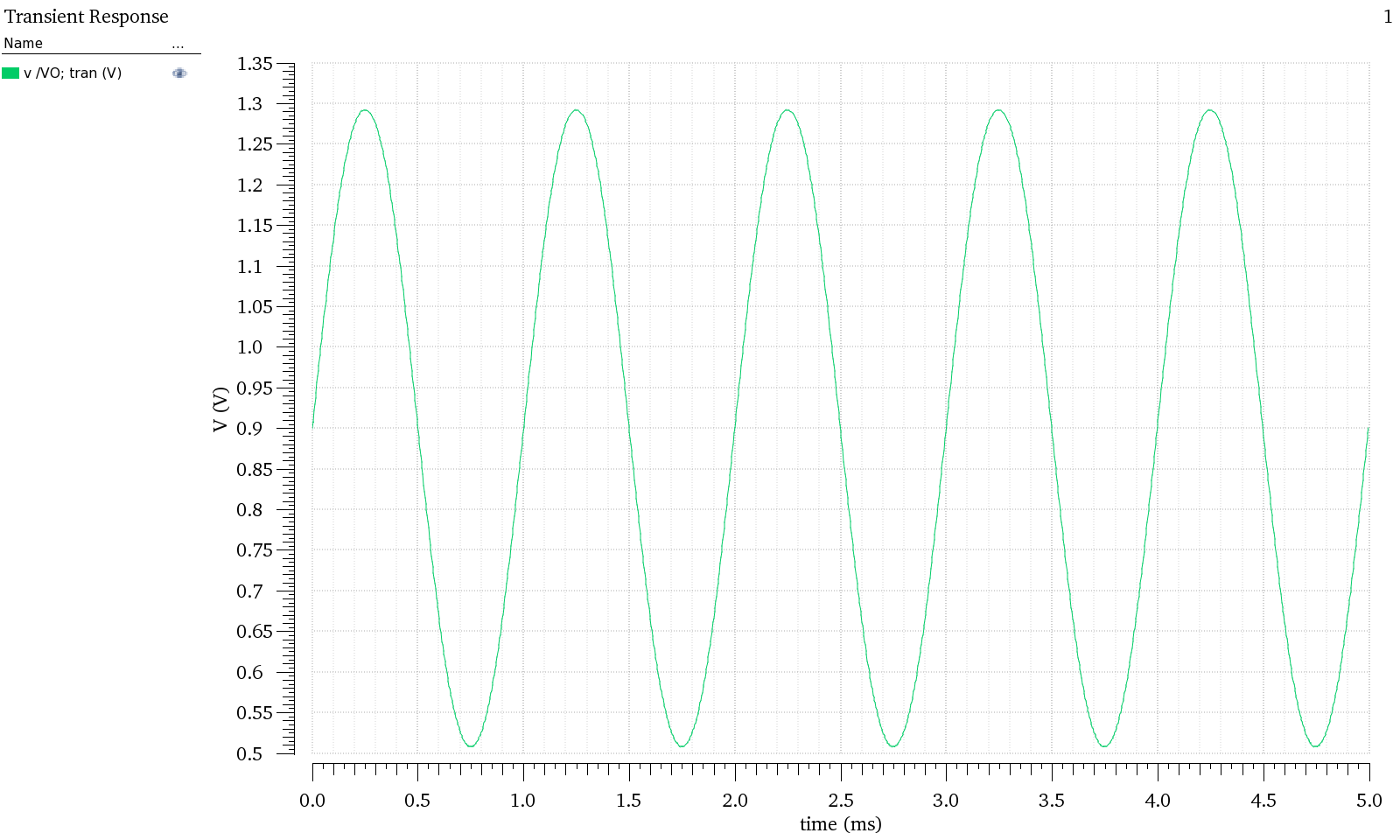

Simulation Results

UGBW: 156MHz

PM: 67.3 degree

Gain: 61.6dB

CMRR: 110.74dB

PSRR+: 61.04dB

PSRR-: 87.57dB

Slew Rate+: 123V/us

Slew Rate-: 408 V/us

Output Swing: 0.5~1.3V

Layout

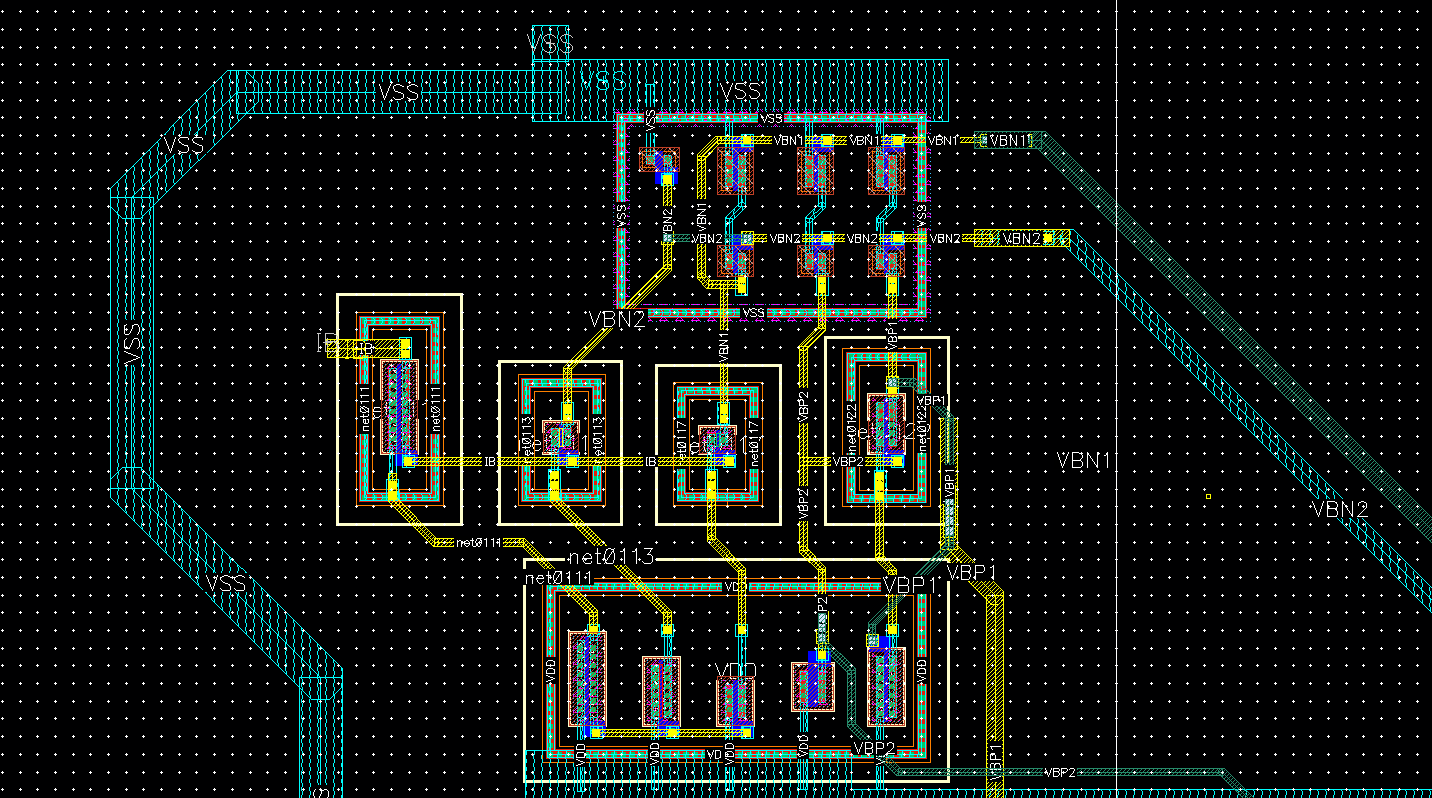

Layout (Bias Circuit)

The End

deck

By aic999

deck

- 515