컴퓨터아키텍처

Computer Architecture

2016-04-28

MIPS Pilpeline

과제 제출 안내

- Google Drive 공유 폴더를 통해 (종이 X, 메일 X)

-

[새로 만들기] 버튼을 눌러

CA16<이름><학번> 폴더를 만들고 (예: CA16김연아123456)

만들어진 폴더를 우클릭하여 나오는 드롭메뉴에서

폴더 공유설정으로 kyagrd@gmail.com 에게 공유 (편집권한) - Google 메일 계정만 있으면 Google Drive 서비스 이용 가능

- Google 메일 계정은 무료로 만들 수 있으며

참고로 안드로이드 스마트폰 사용자는 누구나 이미 보유

MIPS 파이프라인 실습 도구

- WinMIPS64 활용 http://indigo.ie/~mscott/

- 문법이 책의 32-bit MIPS 시뮬레이터인 SIPM과 약간 다름

학과장학금 안내

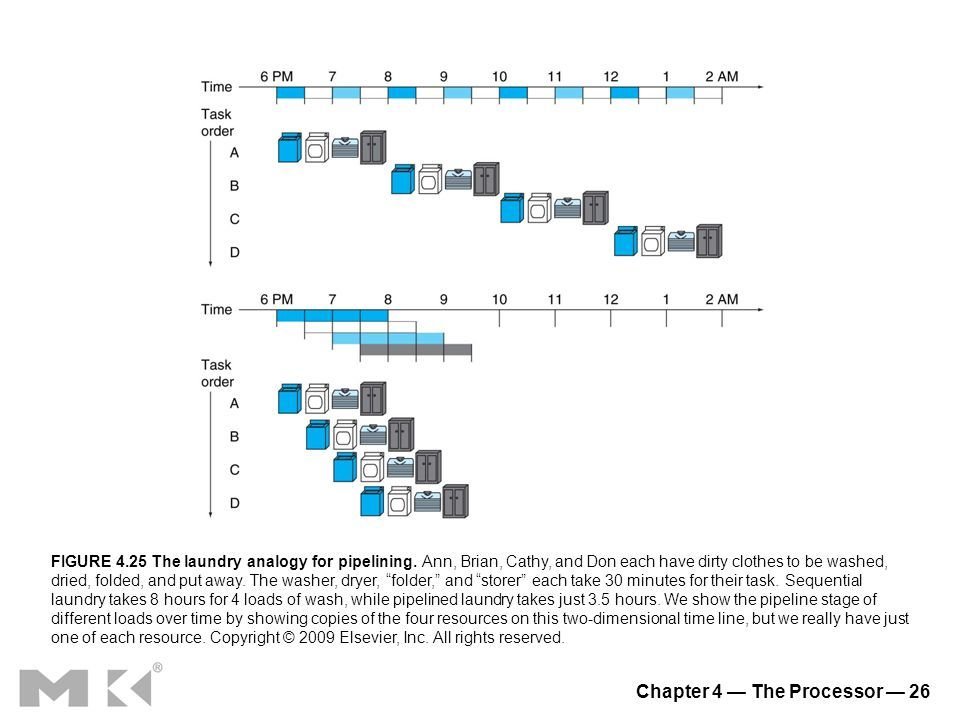

세탁 파이프라인 비유

Pipelining

- Instruction-Level Parallelism

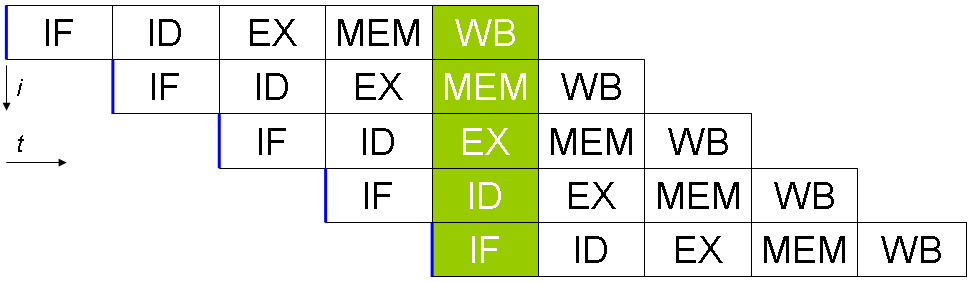

- MIPS에서 명령(instruction)을 수행하는 5 단계(5 stages)

- IF (Instruction Fetch): text/instructon 메모리에서 명령 가져옴

- ID (Instruction Decode and Register Fetch):

명령을 분석하여 필요한 레지스터 값을 읽어옴

(immediate값인 경우 명령에서 바로 읽어옴) - EX (Execute or Address Calculation):

연산 수행 또는 메모리 주소 계산, 다음 PC 계산 - MEM (Memory Access) data 메모리 읽기/쓰기

- WB (Write Back) 레지스터에 결과값 쓰기

- 교과서의 고대적 MIPS는 최대 5명령까지 pipelining

- ARMv8 아키텍처인 ARM Cortex-A57 쿼드코어 CPU는

코어 1개당 최대 128개 명령까지 pipelining

http://www.arm.com/products/processors/cortex-a/cortex-a57-processor.php

이상적인 Pipeline 성능 향상: 충분히 많은 명령을 수행했을 때

- 파이프라인 단계(stage) 수만큼 명령 수행 시간 향상 기대

- 이상적인 경우 2단계면 2배, 5단계면 5배 향상 기대

\text{Time between instructions}_\text{pipelined}

Time between instructionspipelined

= \frac{\text{Time between instructions}_\text{nonpipelined}}{\text{Number of pipeline stages}}

=Number of pipeline stagesTime between instructionsnonpipelined

Data

Text

4

교과서 4.6장 (p. 274부터) 나오는 이런 그림들 이해할 수 있어야 함

할일없는 pipeline stage도 있다

- IF, ID는 모든 명령에 관계없이 기본적으로 필요

- lw 명령은 모든 stage에서 할일이 있다

- sw 명령은 WB에서 할일이 없다

- 메모리를 참조 안하는 연산은 MEM에서 할일이 없다

- nop는 EX, WB, MEM에서 할일이 없다

- 할일없는 stage에서도 시간을 보내야 하는 이유는?

- 동시에 두 명령의 WB 할 수 없게 되어 있으므로

- 명령 하나만 있을 때 자체적으로가 아니라

앞서 처리하고 있던 다른 명령들 때문에

할일이 지연(stall)되는 경우도 있다

Pipeline Hazard

다음 clock cycle에 다음 stage 수행을 못하게 지연(stall)되어

이상적인 파이프라인 성능 향상을 방해하는 상황 발생

- Structural Hazard: 하드웨어의 설계상 문제로 인한 한계

세탁기 비유에서 세탁기, 건조기 따로 쓰는 대신

건조기일체형 드럼세탁기를 쓴다고 생각해 보라 - Data Hazard: 이전 명령의 연산 결과에 뒤이은 명령이 의존

- 레지스터 값에 의존하는 경우는 forwarding(혹은 bypassing)으로 하드웨어적으로 지연(stall) 해소 가능

- 메모리에 들어있는 값에 의존하는 경우는 forwarding을 하더라도 메모리에서 읽어올 때까지 지연(stall) 불가피

- Control Hazard: 순차적이지 않은 PC이동, 즉 branch나 jump 명령 다음에 읽어들일 명령을 미리 알 수 없는 경우

- branch prediction으로 상당부분 개선 가능

컴퓨터아키텍처

By 안기영 (Ahn, Ki Yung)

컴퓨터아키텍처

2016-04-28

- 2,339