FPGA task

Task overview

- The goal is to sort 32-bit unsigned numbers in a window of size N and output the three highest of each window.

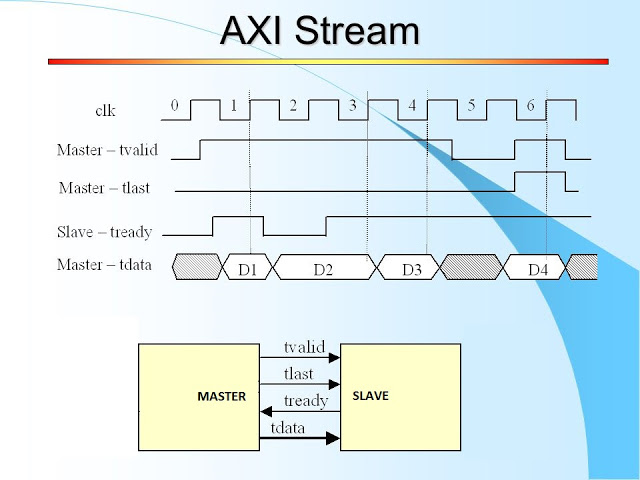

- Our stream protocol is AXI (VALID + READY + DATA + LAST)

Task overview: AXI

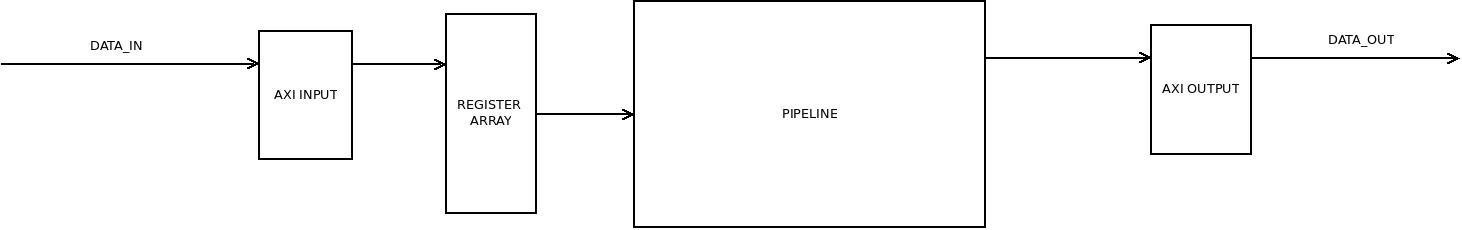

Design proposal

- Sorting is made using a pipelined sorting network (Mergesort) with 7 stages and 8 inputs.

- Storage is only a register array with 8 positions.

- Comparators in the pipeline have a register to save the highest numbers in the window.

- There is a global window counter to output only when it's expected.

Design proposal

Block diagram overview

Design proposal

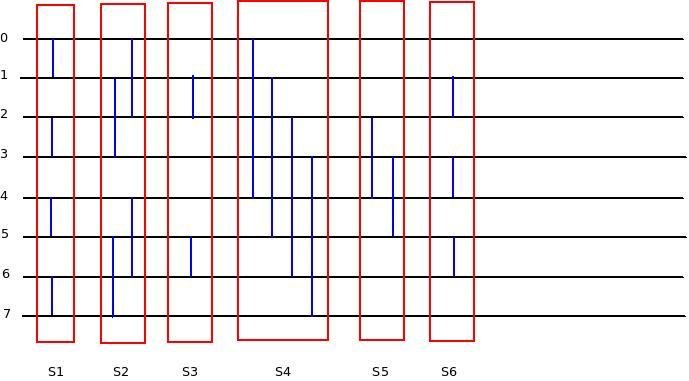

Staged pipeline

So far...

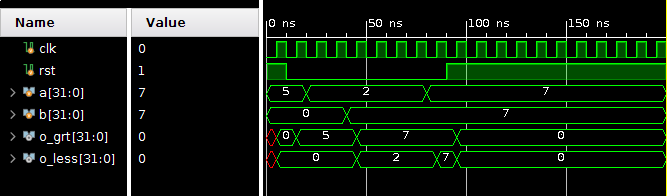

- Implemented and tested: Comparators, stages and pipeline.

- Next pictures are some of our behavioural simulations.

So far...

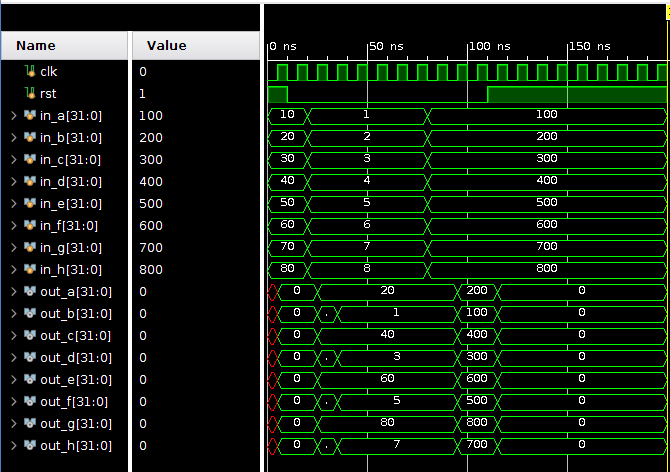

Comparator test

So far...

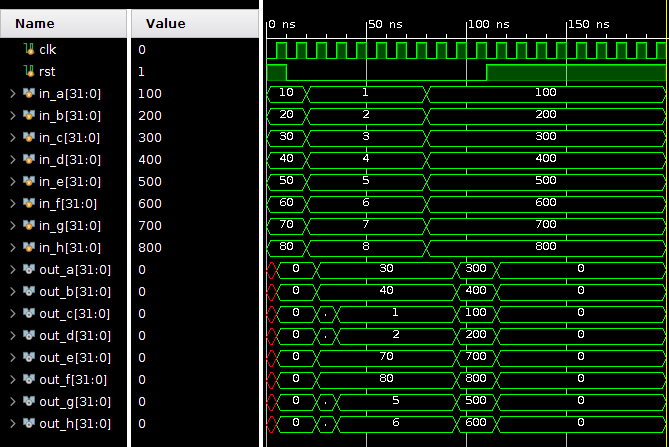

Stage 1 test

So far...

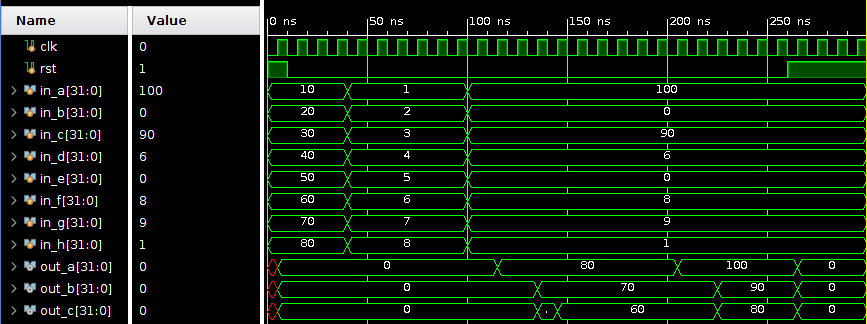

Stage 2 test

So far...

Pipeline test

To be implemented

- AXI Stream source/destination.

- Register array.

- Main module (global window counter).

Issues/Concerns

- Sorting timing is not consistent (should the pipeline output all three numbers at once?)

- Our register array size might be a bottleneck in high-speed transmission.

deck

By samgh96

deck

- 112