RISC

Design Concept

-

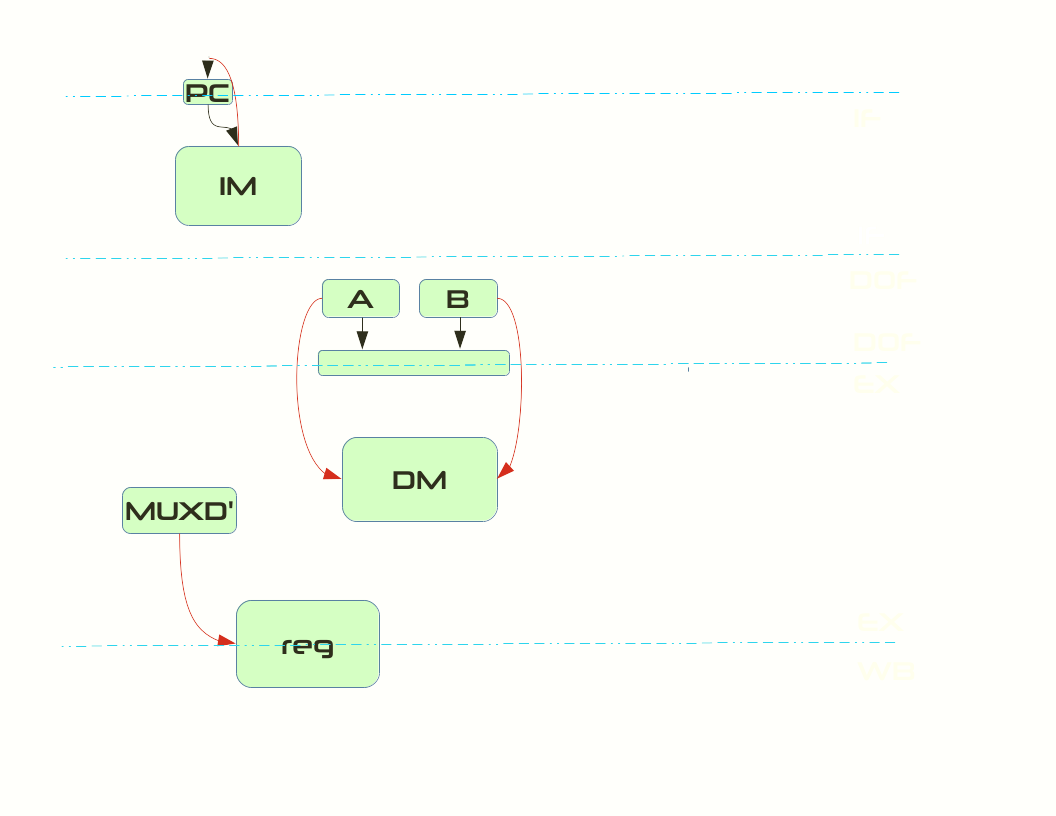

4 Stage pipeline

-

Design mostly according the handouts

-

Some problem need to deal with

-

Memory and Register Read need one more cycle

-

Synthesis library don't provide preload

Design Concept

-

Connect the memory address with previous stage

-

When the posedge clock trigger, can get right data without another cycle

-

The register read don't need another clk, so just care the WB stage

Design Concept

Preload

-

In order to put the memory in risc, testbench will load memory first

-

The other signal loading to determinate the memory is loaded by testbench or instruction

Forwarding

-

If the DOF stage need EX stage register, need forwarding

-

Use comp module to determinate select whether need take the forwarding data

-

WB stage may implement forwarding to reduce the cycle time. However, no time to implement

Branch Prediction

-

If branch happened, need flush

-

Because the memory problem, flush need delay a cycle

Completion

Completion

-

Fully 4 stages pipeline (normal)

-

Forwarding instead of memory stall to deal with hazard (normal)

-

Branch prediction (normal)

with verilog(nightmare) -

Synthesis with memory (epic)

-

Compile flag of design_vision (normal)

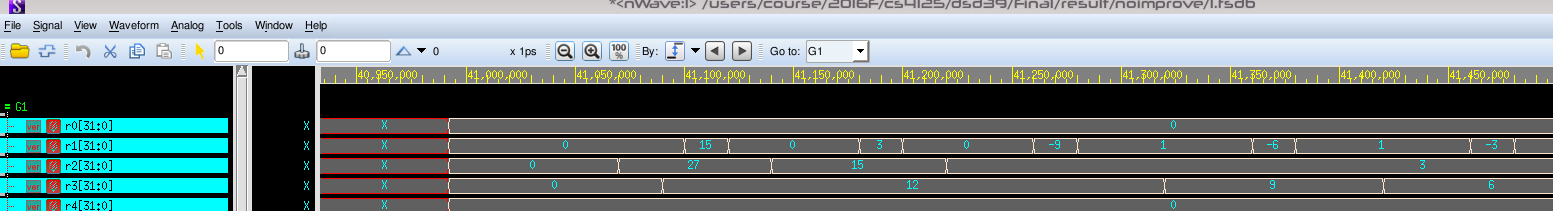

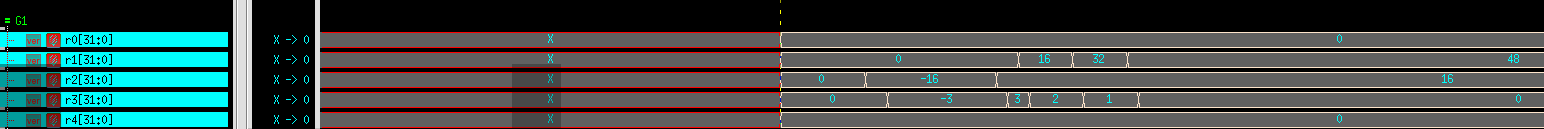

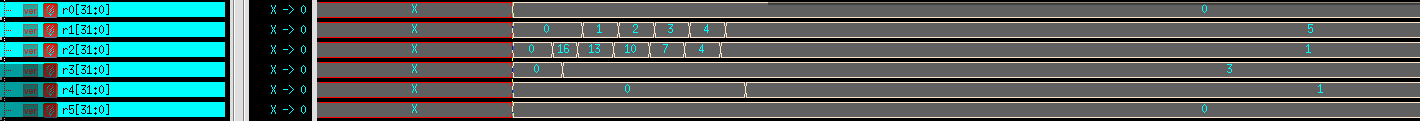

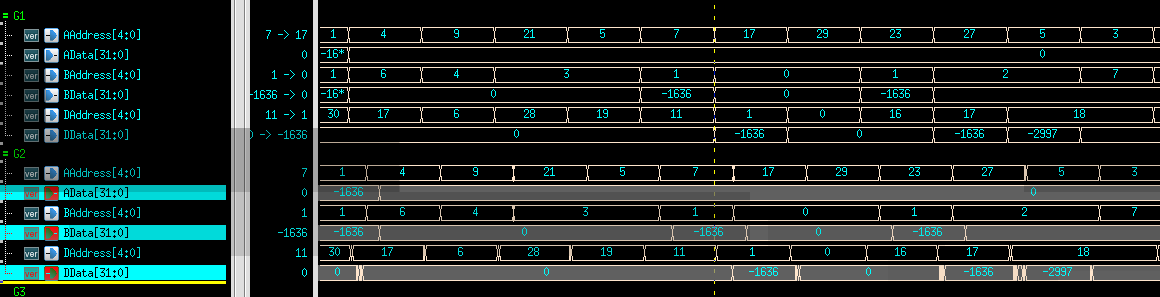

Test

Provide testcase

-

The 1, 2, 3 correctness is correct

-

The other testcase only check the synthesis v.s RTL result

-

Generate Random testcase

2048 random data

2048 random valid instruction

Other

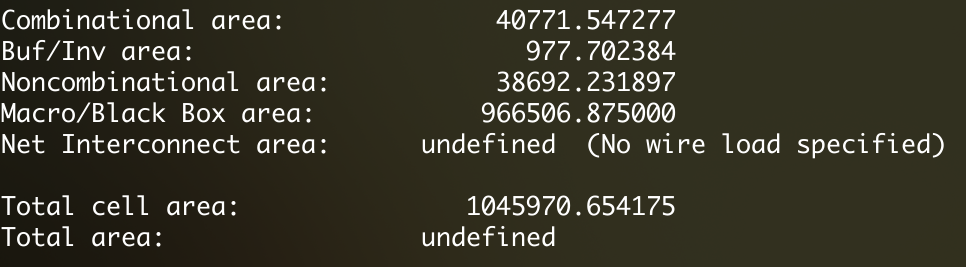

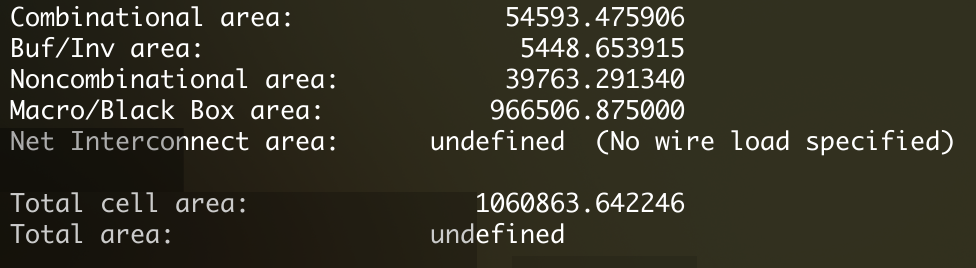

Compile flag

Text

-

clock period 10

-

Area reduce 25%

RISC

By zlsh80826

RISC

- 620